## Anil Kanduri

# Adaptive Knobs for Resource Efficient Computing

TURKU CENTRE for COMPUTER SCIENCE

TUCS Dissertations No 236, December 2018

## Adaptive Knobs for Resource Efficient Computing

## Anil Kanduri

To be presented with the permission of the Faculty of Science and Engineering of the University of Turku for public criticism on December 13, 2018, at 12 noon in auditorium Agora XXI.

University of Turku

Department of Future Technologies

20014 TURUN YLIOPISTO

FINLAND

2018

#### **Supervisors**

Professor Pasi Liljeberg Department of Future Technologies University of Turku, Finland

Adjunct Professor Amir M. Rahmani Department of Future Technologies University of Turku, Finland Marie Curie Global Fellow University of California Irvine, USA and TU Wien, Austria

Professor Hannu Tenhunen Department of Future Technologies University of Turku, Finland

#### **Reviewers**

Dr. Gianluca Palermo Associate Professor Department of Electronics, Information and Bio Engineering Politecnico di Milano Italy

Dr. Elaheh Bozorgzadeh Associate Professor Department of Computer Science University of California, Irvine USA

#### **Opponent**

Professor Jari Nurmi Department of Electronics and Communications Engineering Tampere University of Technology Finland

ISBN 978-952-12-3775-1 ISSN 1239-1883

The originality of this thesis has been checked in accordance with the University of Turku quality assurance system using the Turnitin Originality Check service.

## **Abstract**

Performance demands of emerging domains such as artificial intelligence, machine learning and vision, Internet-of-things etc., continue to grow. Meeting such requirements on modern multi/many core systems with higher power densities, fixed power and energy budgets, and thermal constraints exacerbates the run-time management challenge. This leaves an open problem on extracting the required performance within the power and energy limits, while also ensuring thermal safety. Existing architectural solutions including asymmetric and heterogeneous cores and custom acceleration improve performance-per-watt in specific design time and static scenarios. However, satisfying applications' performance requirements under dynamic and unknown workload scenarios subject to varying system dynamics of power, temperature and energy requires intelligent run-time management.

Adaptive strategies are necessary for maximizing resource efficiency, considering i) diverse requirements and characteristics of concurrent applications, ii) dynamic workload variation, iii) core-level heterogeneity and iv) power, thermal and energy constraints. This dissertation proposes such adaptive techniques for efficient run-time resource management to maximize performance within fixed budgets under unknown and dynamic workload scenarios. Resource management strategies proposed in this dissertation comprehensively consider application and workload characteristics and variable effect of power actuation on performance for pro-active and appropriate allocation decisions. Specific contributions include i) run-time mapping approach to improve power budgets for higher throughput, ii) thermal aware performance boosting for efficient utilization of power budget and higher performance, iii) approximation as a run-time knob exploiting accuracyperformance trade-offs for maximizing performance under power caps at minimal loss of accuracy and iv) co-ordinated approximation for heterogeneous systems through joint actuation of dynamic approximation and power knobs for performance guarantees with minimal power consumption.

The approaches presented in this dissertation focus on adapting existing mapping techniques, performance boosting strategies, software and dynamic approximations to meet the performance requirements, simultaneously considering system constraints. The proposed strategies are compared against relevant state-of-the-art run-time management frameworks to qualitatively evaluate their efficacy.

## Tiivistelmä

Suorituskykyvaatimukset kasvavat jatkuvasti uusilla tietotekniikan aloilla, kuten tekoäly, koneoppiminen, konenäkö ja esineiden internet. Näiden vaatimusten täyttäminen moderneilla moniydinjärjestelmillä, joissa on korkea tehotiheys, rajalliset teho- ja energiabudjetit ja lämpötilarajoitteita, tekee järjestelmän käytönaikaisen hallinnan haastavaksi. Ongelmaksi muodostuu, miten saada järjestelmistä tarvittava suorituskyky, huomioiden samalla teho- ja energiarajat sekä turvallisuus lämpötilan osalta. Olemassa olevat arkkitehtuuriratkaisut, kuten asymmetriset ja heterogeeniset ytimet ja räätälöity kiihdyttäminen, parantavat suorituskykyä wattia kohden staattisissa skenaarioissa. Sovellusten suorituskykyvaatimusten täyttäminen dynaamisissa ja ennalta tuntemattomissa kuormitustilanteissa, joissa tehon, lämpötilan ja energian järjestelmädynamiikka vaihtelee, vaatii kuitenkin älykästä ajoajan hallintaa.

Adaptiiviset strategiat ovat välttämättömiä resurssitehokkuuden maksimoimiseksi, huomioiden i) samanaikaisten sovellusten vaihtelevat vaatimukset ja ominaisuudet, ii) dynaaminen kuormituksen vaihtelevuus, iii) heterogeenisyys ytimien tasolla ja iv) tehon, lämpötilan ja energian rajoitteet. Tämä väitöskirja esittää nämä seikat huomioivia adaptiivisia tekniikoita järjestelmän käytönaikaiseen resurssihallintaan dynaamisissa kuormitustilanteissa. Väitöskirjassa esiteltävät resurssinhallintastrategiat huomioivat kattavasti sovellusten ja kuormitusten ominaispiirteet sekä tehoaktuaation vaihtelevat vaikutukset suorituskykyyn. Väitöskirjan spesifiset kontribuutiot käsittävät mm. i) ajoajan kartoitusmenettelyn tehobudjettien parantamiseksi korkeammalla suoritusteholla, ii) lämpötilan huomioivan suorituskyvyn tehostamisen korkeamman suorituskyvyn saavuttamiseksi, iii) approksimaatiolaskennan soveltaminen suorituskyvyn optimoimiseksi ja iv) heterogeenisten järjestelmien dynaaminen approksimaatio.

Väitöskirjan esittämät menetelmät keskittyvät olemassa olevien kartoitustekniikoiden, suorituskyvyn parannusstrategioiden, sovellusten ja dynaamisten approksimaatioiden adaptoimiseen niin, että suorituskykyvaatimukset täytetään pysyen samalla järjestelmärajoitteiden puitteissa. Ehdotettuja strategioita verrataan viimeisimpiin ja kehittyneimpiin käytönaikaisiin järjestelmänhallintamenetelmiin niiden tehokkuuden kvalitatiiviseksi arvioimiseksi.

## Acknowledgement

I thank my supervisor Prof. Pasi Liljeberg for shepherding this research by providing an organized environment, stability and freedom. His flexible approach eased my study period and the process of this dissertation. I also thank my cosupervisor and advisor Dr. Amir Rahmani for his guidance throughout the course of this research. His emphasis on identifying relevant research problems and encouragement in pursuing novel solutions shaped my learning process. He helped me in expressing and presenting different ideas with clarity, and forming an overall organized work structure.

Both the supervisors helped to foster collaborations with different research groups, which created valuable working experiences. I extend my regards to all the collaborators and co-authors - Prof. Nikil Dutt, Prof. Axel Jantsch, Prof. Cristiana Bolchini, Prof. Muhammad Shafique and Prof. Hannu Tenhunen - for exchange of ideas, providing their insights and comments in shaping my work.

I am indebted to Prof. Antonio Miele for his guidance, mentorship and the invaluable time he gave to evaluate my work. His hands-on approach and lively presence made the collaboration and the research visits thoroughly enjoyable. Dr. Hashem Haghbayan helped me to identify my strengths and weaknesses, and tried to make me understand many things in and out of research. I express my deepest gratitude to Hashem, for his belief and everything he has done for me.

This research was supported by Academy of Finland projects, University of Turku Graduate School fellowship, University of Turku Foundation, Nokia Foundation and TES Foundations' grants. I thank these organizations for their generosity.

I thank the dissertation reviewers Prof. Gianluca Palermo for the valuable comments and acceptance with honors, and Prof. Elaheh Bozorgzadeh for the feedback and acceptance.

I appreciate all the friends whose compassion kept my sanity. Finally, I thank my parents Pardha Saradhi and Andal, and my sister Swathi for their continued support, belief and encouragement. They have always been there to cheer me up, listen to me and gave the much needed advice.

## List of original publications

The work presented in this dissertation is based on the publications listed below:

Paper I

**Anil Kanduri**, Hashem Haghbayan, Amir Rahmani, Axel Jantsch, Pasi Liljeberg, Hannu Tenhunen, "Dark Silicon Aware Run-time Mapping for Many-core Systems: A Patterning Approach", in IEEE International Conference on Computer Design (ICCD 2015), USA.

Paper II

Anil Kanduri, Hashem Haghbayan, Amir Rahmani, Muhammad Shafique, Axel Jantsch and Pasi Liljeberg, "adBoost: Thermal Aware Performance Boosting through Dark Silicon Patterning", in IEEE Transactions on Computer, (IEEE-TC 2018)

Paper III

Anil Kanduri, Hashem Haghbayan, Amir Rahmani, Pasi Liljeberg, Axel Jantsch, Nikil Dutt and Hannu Tenhunen, "Approximation Knob: Power Capping Meets Energy Efficiency", in IEEE/ACM International Conference on Computer Aided Design (ICCAD 2016), USA.

Paper IV

Anil Kanduri, Hashem Haghbayan, Amir Rahmani, Pasi Liljeberg, Axel Jantsch, Hannu Tenhunen and Nikil Dutt, "Accuracy-Aware Power Management for Many-Core Systems Running Error-Resilient Applications", in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, (IEEE-TVLSI 2017).

Paper V

**Anil Kanduri**, Antonio Miele, Amir Rahmani, Pasi Liljeberg, Cristiana Bolchini and Nikil Dutt, "Approximation-Aware Coordinated Power/Performance Management of Heterogeneous Multi-cores", in ACM/IEEE Design Automation Conference (DAC 2018), USA.

## **List of Figures**

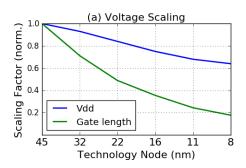

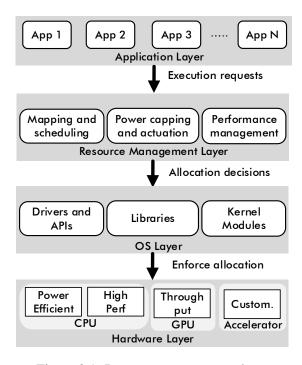

| 1.1 | sociation, 2013]. (a). Slack voltage scaling and (b). Rise in power density                                                                                                                                                                                                                                                     | 4  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

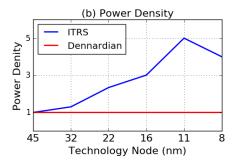

| 1.2 | Reduced on-chip activity with technology node scaling and dark silicon [Semiconductor Industry Association, 2013]                                                                                                                                                                                                               | 5  |

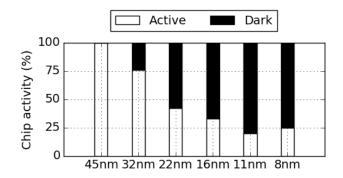

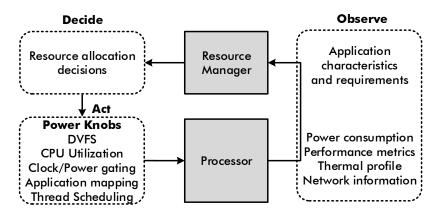

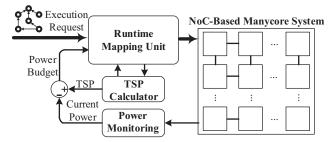

| 2.1 | Resource management layer                                                                                                                                                                                                                                                                                                       | 12 |

| 2.2 | Run-time resource management in ODA loop                                                                                                                                                                                                                                                                                        | 13 |

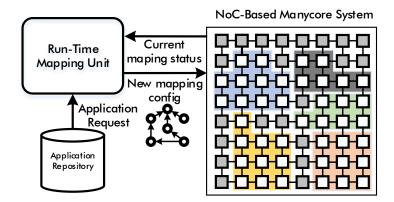

| 2.3 | Application mapping overview                                                                                                                                                                                                                                                                                                    | 15 |

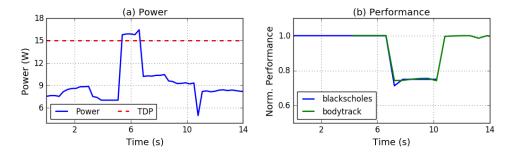

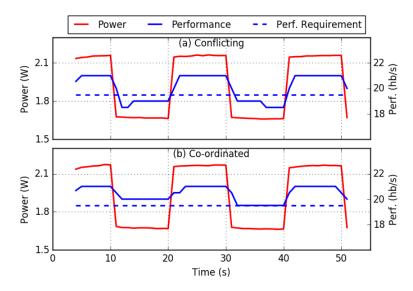

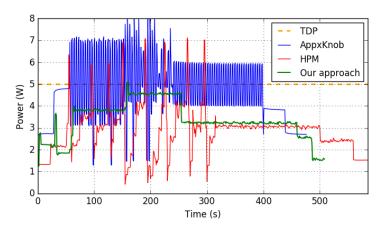

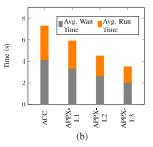

| 2.4 | Power capping in a dynamic workload scenario. (a) Power consumption (b) Normalized performance. TDP is set to 15W and blackscholes and bodytrack applications are simulated concurrently.                                                                                                                                       | 18 |

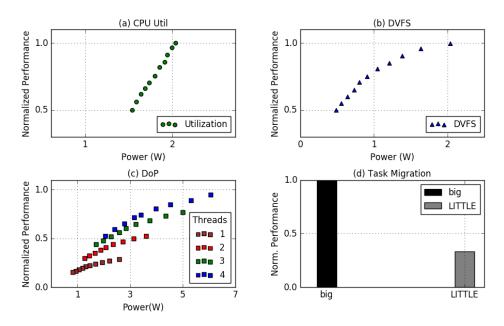

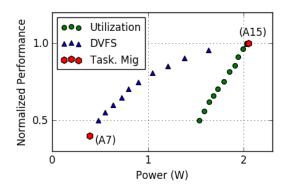

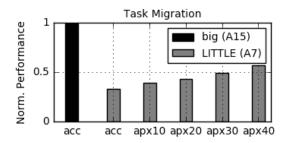

| 2.5 | Power-performance Pareto-space with different knobs. (a) CPU Utilization, (b) DVFS, (c) Degree of parallelism, (d) Task migration. Experiments were run on quad-core ARM A15 for k-means micro kernel.                                                                                                                          | 20 |

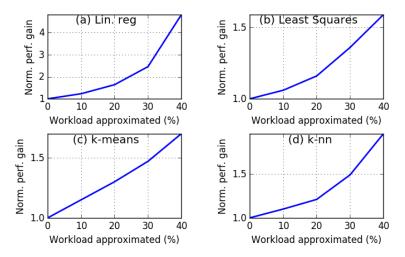

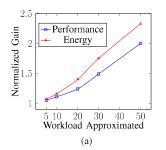

| 2.6 | Performance gains with approximation. (a) Linear regression, (b) Least squares, (c) k-means, (d) k-nearest neighbors. Workload approximated corresponds to the percentage of loops skipped                                                                                                                                      | 21 |

| 2.7 | Overview of generic system architecture                                                                                                                                                                                                                                                                                         | 23 |

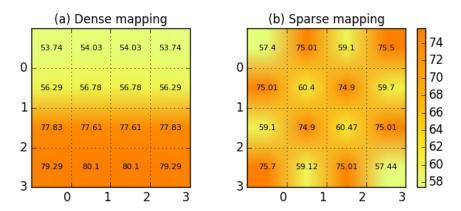

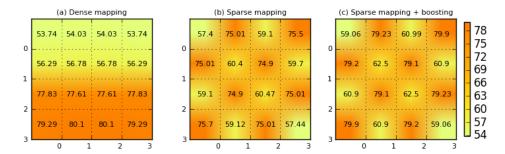

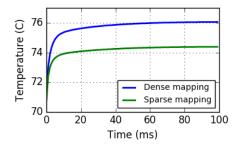

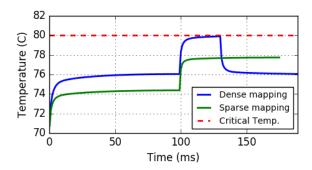

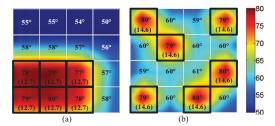

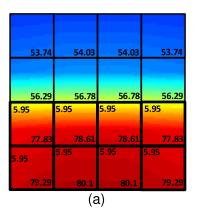

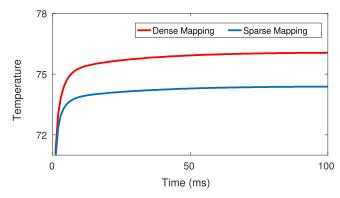

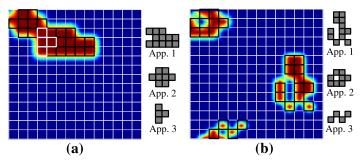

| 3.1 | Effect of mapping on on-chip temperatures. (a). Dense mapping configuration, application is mapped contiguously on rows 2 and 3, (b). Sparse mapping configuration, application is mapped sparsely on every alternative core. Each tile shows temperature (in °C) of the core                                                   | 26 |

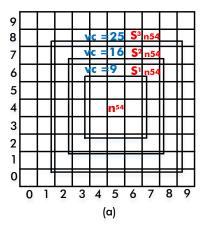

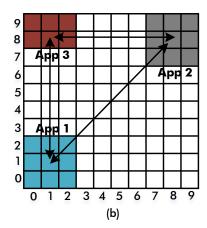

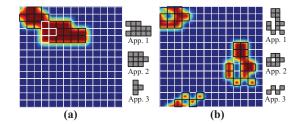

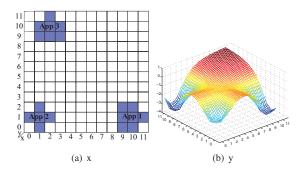

| 3.2 | Region selection strategy with criteria of: (a) Number of free nodes around a given first node. Here, 3 different square regions (S) and VCs possible for the same first node (n) are shown. (b) Distance from other active cores. Here, applications App1, App2 and App3 being mapped progressively based on distance is shown | 29 |

| 3.3 | Hierarchical view of proposed approach                                                                                                                                                                                                                                                                                          | 31 |

|     |                                                                                                                                                                                                                                                                                                                                 |    |

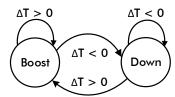

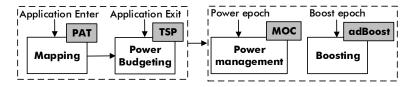

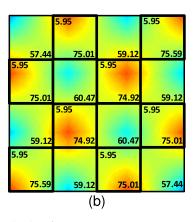

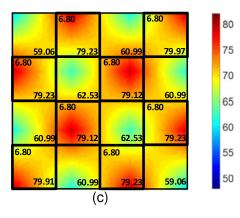

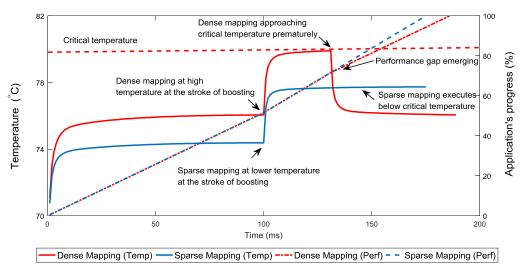

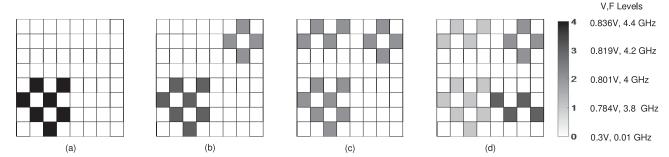

| Thermal headroom for boosting with sparse mapping. (a) Dense mapping, (b) Sparse mapping without boosting, (c) Sparse map-                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                  | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                  | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                  | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                  | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                  | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                  | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                  | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| * * **                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                  | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

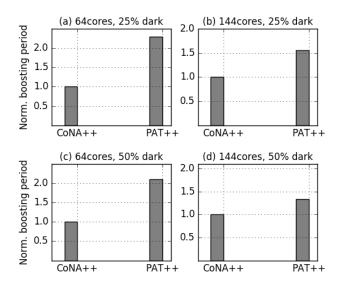

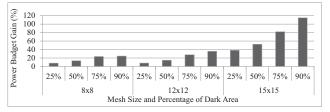

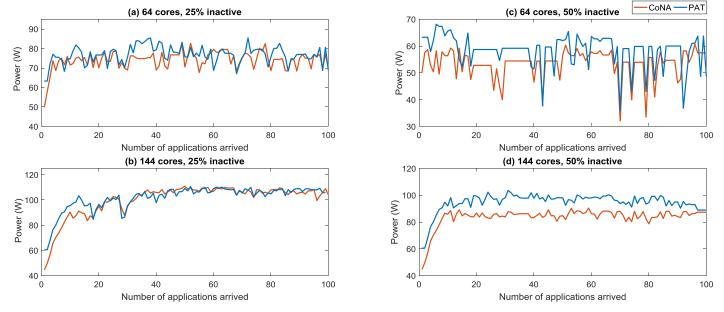

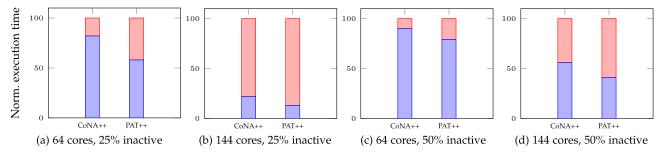

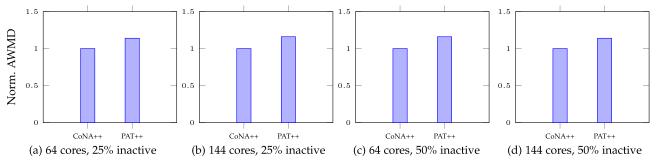

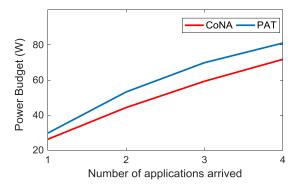

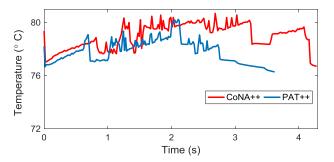

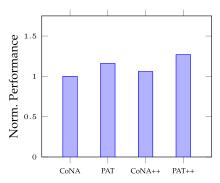

| PAT++) for different configurations                                                                                                                                                                                                                                                                              | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

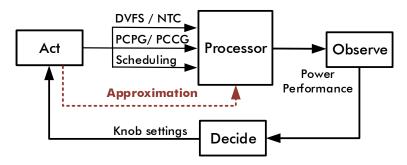

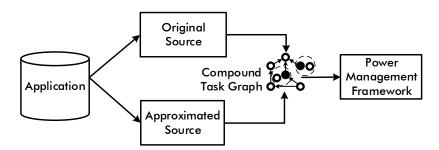

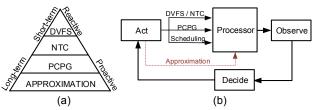

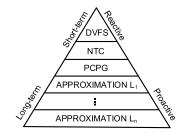

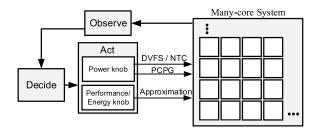

| Approximation as a resource management knob                                                                                                                                                                                                                                                                      | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

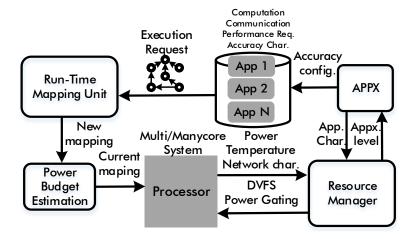

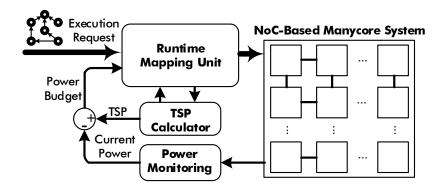

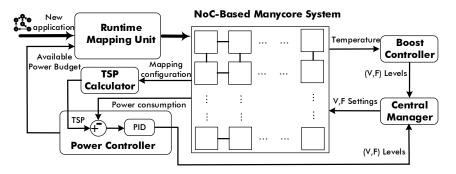

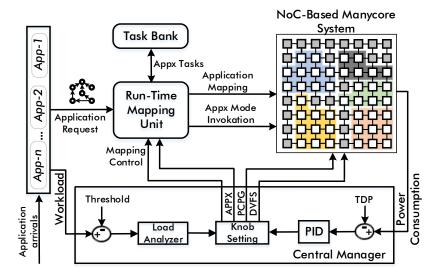

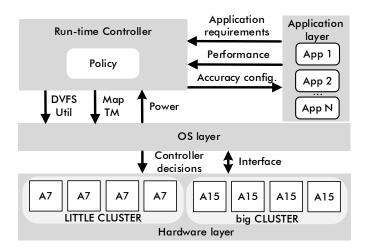

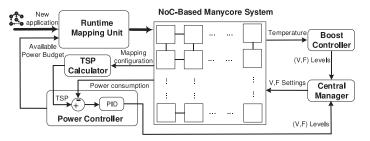

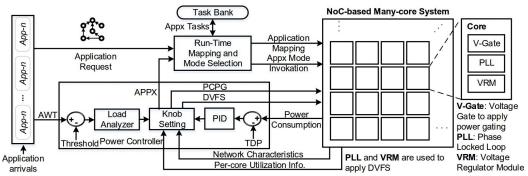

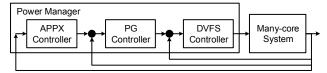

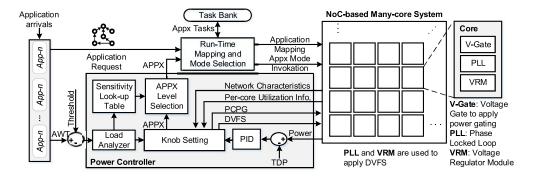

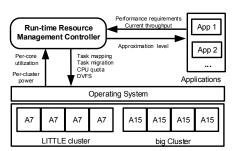

| System architecture                                                                                                                                                                                                                                                                                              | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

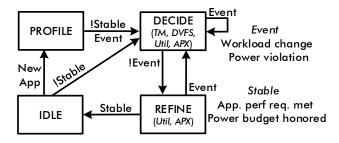

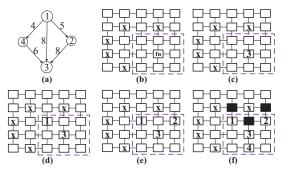

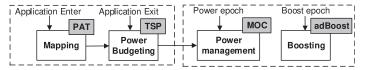

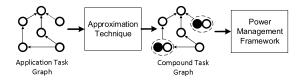

| Workflow of proposed approach. Solid filled tasks are approximable.                                                                                                                                                                                                                                              | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| tasks                                                                                                                                                                                                                                                                                                            | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                  | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                  | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

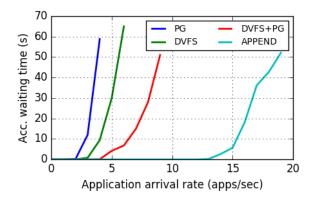

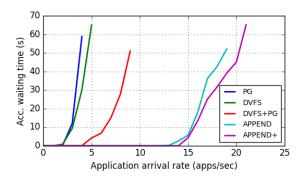

|                                                                                                                                                                                                                                                                                                                  | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

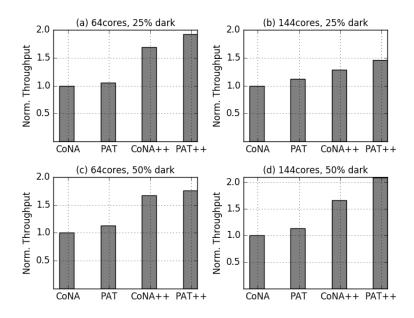

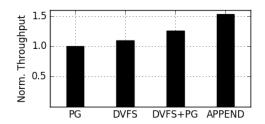

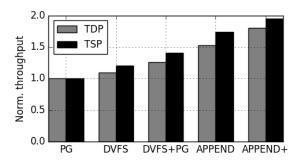

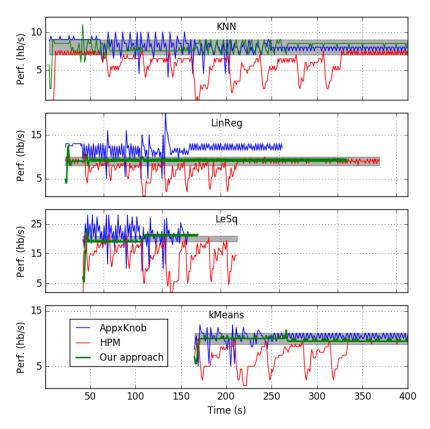

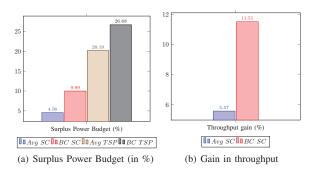

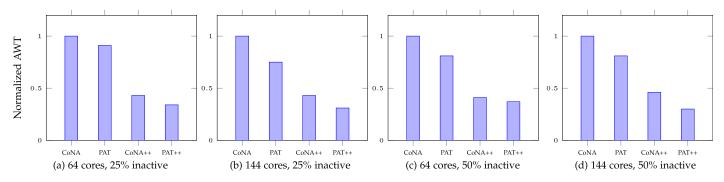

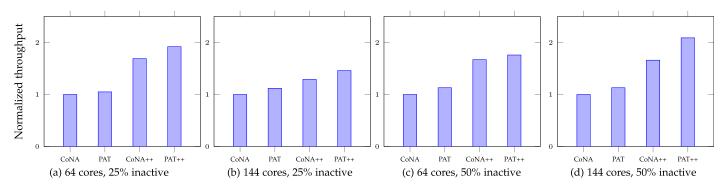

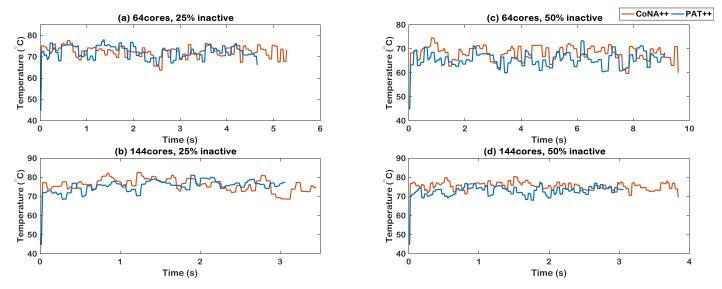

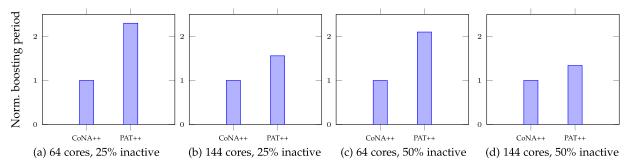

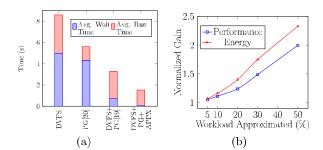

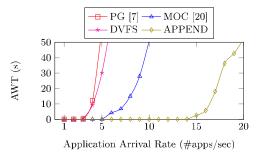

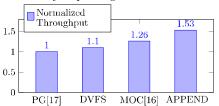

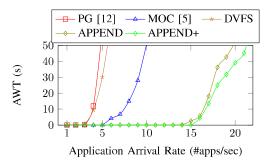

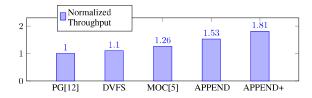

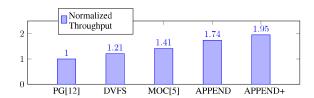

| Normalized throughput with the proposed approach                                                                                                                                                                                                                                                                 | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

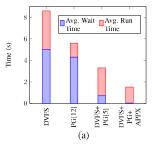

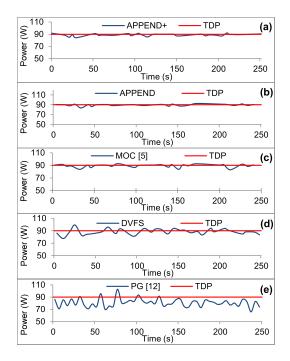

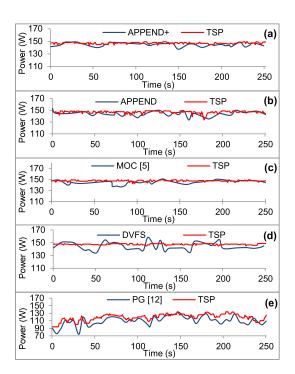

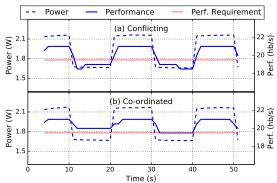

| Power-performance behavior with different knobs                                                                                                                                                                                                                                                                  | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

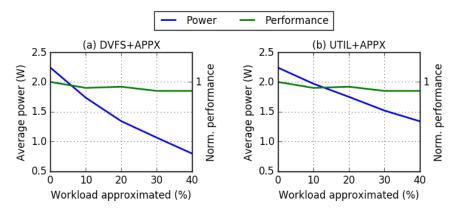

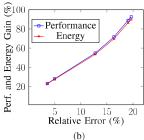

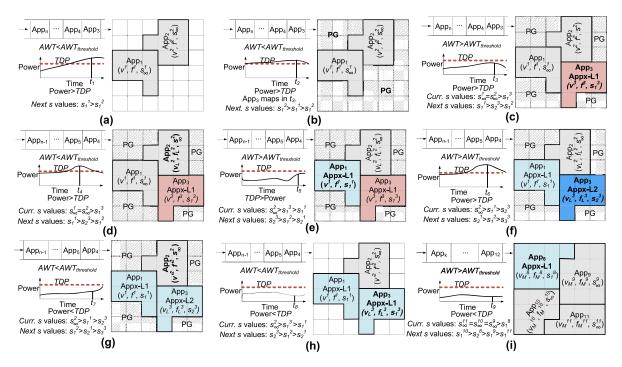

| Power-performance behavior with joint actuation of approximation and power knobs. (a) DVFS and APPX - frequency scaled from 1.8GHz to 1GHz in steps of 0.2GHz, (b) CPU Utilization and APPX - utilization scaled down in steps of 10%. In both cases, APPX corresponds to 0%-40% of loops skipped over 1 million |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

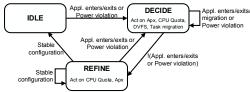

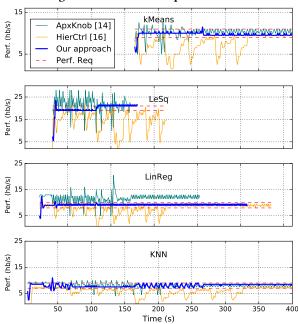

| pairs of least squares kernel                                                                                                                                                                                                                                                                                    | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |