#### TURUN YLIOPISTON JULKAISUJA ANNALES UNIVERSITATIS TURKUENSIS

SARJA - SER. A I OSA - TOM. 429

ASTRONOMICA - CHEMICA - PHYSICA - MATHEMATICA

# Exploring Adaptive Implementation of On-Chip Networks

by

Masoud Daneshtalab

TURUN YLIOPISTO UNIVERSITY OF TURKU Turku 2011 From the Laboratory of Embedded Computer Systems Department of Information Technology University of Turku Turku, Finland

&

Graduate School in Electronics, Telecommunication and Automation (GETA) Aalto University Helsinki, Finland

#### Supervisors

Professor Hannu Tenhunen Adjunct Professor Juha Plosila Adjunct Professor Pasi Liljeberg Department of Information Technology University of Turku Turku, Finland

#### Reviewers

Professor José Flich School of Engineering in Computer Science Technical University of Valencia Valencia, Spain

Professor Timo D. Hämäläinen Department of Computer Systems Technical University of Tampere Tampere, Finland

#### Opponent

Professor Thomas Hollstein Department of Computer Engineering Tallin University of Technology Tallin, Estonia

ISBN 978-951-29-4786-7 (PRINT) ISBN 978-951-29-4787-4 (PDF) ISSN 0082-7002 Painosalama Oy – Turku, Finland 2011

### **Abstract**

As technology geometries have shrunk to the deep submicron regime, the communication delay and power consumption of global interconnections in high performance Multi-Processor Systems-on-Chip (MPSoCs) are becoming a major bottleneck. The Network-on-Chip (NoC) architecture paradigm, based on a modular packet-switched mechanism, can address many of the on-chip communication issues such as performance limitations of long interconnects and integration of large number of Processing Elements (PEs) on a chip. The choice of routing protocol and NoC structure can have a significant impact on performance and power consumption in on-chip networks. In addition, building a high performance, area and energy efficient on-chip network for multicore architectures requires a novel on-chip router allowing a larger network to be integrated on a single die with reduced power consumption. On top of that, network interfaces are employed to decouple computation resources from communication resources, to provide the synchronization between them, and to achieve backward compatibility with existing IP cores.

Three adaptive routing algorithms are presented as a part of this thesis. The first presented routing protocol is a congestion-aware adaptive routing algorithm for 2D mesh NoCs which does not support multicast (one-to-many) traffic while the other two protocols are adaptive routing models supporting both unicast (one-to-one) and multicast traffic. A streamlined on-chip router architecture is also presented for avoiding congested areas in 2D mesh NoCs via employing efficient input and output selection. The output selection utilizes an adaptive routing algorithm based on the congestion condition of neighboring routers while the input selection allows packets to be serviced from each input port according to its congestion level. Moreover, in order to increase memory parallelism and bring compatibility with existing IP cores in network-based multiprocessor architectures, adaptive network interface architectures are presented to use multiple SDRAMs which can be accessed simultaneously. In addition, a smart memory controller is integrated in the adaptive network interface to improve the memory utilization and reduce both memory and network latencies.

Three Dimensional Integrated Circuits (3D ICs) have been emerging as a viable candidate to achieve better performance and package density as compared to traditional 2D ICs. In addition, combining the benefits of 3D IC and NoC schemes provides a significant performance gain for 3D architectures. In recent years, inter-layer communication across multiple stacked layers (vertical channel) has attracted a lot of interest. In this thesis, a novel adaptive pipeline bus structure is proposed for inter-layer communication to improve the performance by reducing the delay and complexity of traditional bus arbitration. In addition, two mesh-based topologies for 3D architectures are also introduced to mitigate the inter-layer footprint and power dissipation on each layer with a small performance penalty.

# **Acknowledgments**

"Life is like riding a bicycle. To keep your balance you must keep moving."

- Albert Einstein

The research work presented in this thesis has been carried out in the department of Information Technology, University of Turku from September 2008 to November 2011. This work would not have been possible in three years without the support of many people.

First of all, I would like to express my deepest gratitude to my supervisors, Prof. Hannu Tenhunen, Adj. Prof. Juha Plosila, and Adj. Prof. Pasi Liljeberg, for their excellent guidance, patience, and providing me with an excellent atmosphere for doing research.

I share the credit of this work with my wonderful wife, Masoumeh Ebrahimi, for being a collaborator on almost all my publications and giving the necessary comments and criticism. Moreover, without her love, encouragement, and patience over the years, I would not be able to finish this research work. She is always the first one I would go to whenever I need support, and the first one to share my happiness on my success.

It gives me great pleasure in acknowledging Prof. José Flich from Polytechnic University of Valencia and Prof. Timo D. Hämäläinen from Technical University of Tampere for the detailed reviews and the constructive comments on the manuscript.

I greatly appreciate the financial support for my doctoral studies from the Graduate School in Electronics, Telecommunication and Automation (GETA). This research work was also financially supported by the Nokia Foundation, ST-Micro, and Ulla Tuominen Foundation.

Finally, I would like to thank my parents for their constant love, support, and prayers and dedicate this thesis to them

Turku, November 2011 Masoud Daneshtalab

<sup>&</sup>quot;Imagination is more important than knowledge. Knowledge is limited. Imagination encircles the world."

### **List of Publications**

The work presented in this thesis is based on the following publications:

#### Journal publications:

- M. Daneshtalab, M. Ebrahimi, P. Liljeberg, Juha Plosila, and H. Tenhunen, "Memory-Efficient On-Chip Network with Adaptive Interfaces," IEEE Transaction on Computer-Aided Design of Integrated Circuits and Systems (*IEEE TCAD*) (To appear).

- M. Daneshtalab, M. Ebrahimi, T. C. Xu, P. Liljeberg, and H. Tenhunen, "A generic adaptive path-based routing method for MPSoCs," Journal of Systems Architecture (*JSA-elsevier*), Vol. 57, No. 1, pp. 109-120, 2011.

- M. Daneshtalab, M. Kamali, M. Ebrahimi, S. Mohammadi, A. Afzali-Kusha, and J. Plosila, "Adaptive Input-output Selection Based On-Chip Router Architecture," Journal of Low Power Electronics (*JOLPE*) (To appear).

- M. Daneshtalab, M. Ebrahimi, S. Mohammadi, and A. Afzali-Kusha, "Low distance path-based multicast algorithm in NOCs," Journal of the Institute of Engineering and Technology (*IET Computers and Digital Techniques*), Special issue on NoC, Vol. 3, Issue 5, pp. 430-442, Sep 2009.

- P. Lotfi-kamran, A. Rahmani, M. Daneshtalab, A. Afzali-Kusha, and Z. Navabi, "EDXY A Smart Congestion-Aware and Link Failure Tolerant Routing Algorithm for Network-on-Chips," Journal of Systems Architecture (*JSA-elsevier*), Vol. 56, No. 7, pp. 256-264, Jul 2010.

#### Conference publications:

- M. Daneshtalab, M. Ebrahimi, P. Liljeberg, J. Plosila, and H. Tenhunen, "Cluster-based Topologies for 3D Stacked Architectures," in Proceedings of ACM International Conference on Computing Frontiers (*CF*), pp. 1-3, May 2011, Italy.

- M. Daneshtalab, M. Ebrahimi, P. Liljeberg, J. Plosila, and H. Tenhunen, "High-Performance On-Chip Network Platform for Memory-on-Processor Architectures," in Proceedings of IEEE International Symposium on Reconfigurable Communication-centric Systems-on-Chip (*ReCoSoC*), pp. 1-6, June 2011, France.

- M. Daneshtalab, M. Ebrahimi, P. Liljeberg, Juha Plosila, and H. Tenhunen, "CMIT- A Novel Cluster-based Topology for 3D Stacked Architectures," in Proceedings of 2nd IEEE International 3D System Integration Conference (*3DIC*), pp. 1-5, Nov 2010, Germany.

- M. Daneshtalab, M. Ebrahimi, P. Liljeberg, J. Plosila, and H. Tenhunen, "Input-Output Selection Based Router for Networks-on-Chip," in Proceedings of 9th IEEE International Symposium on VLSI (*ISVLSI*), pp. 92-97, July 2010, Greece.

- M. Daneshtalab, M. Ebrahimi, P. Liljeberg, Juha Plosila, and H. Tenhunen, "A Low-Latency and Memory-Efficient On-hip Network," in Proceedings of 4th IEEE/ACM International Symposium on Network-on-Chip (*NOCS*), pp. 99-106, May 2010, France.

- M. Ebrahimi, M. Daneshtalab, P. Liljeberg, and H. Tenhunen, "HAMUM A Novel Routing Protocol for Unicast and Multicast Traffic in MPSoCs," in Proceedings of 18th IEEE Euromicro Conference on Parallel, Distributed and Network-Based Computing (*PDP*), pp. 525-532, February 2010, Italy.

- M. Ebrahimi, M. Daneshtalab, P. Liljeberg, J. Plosila, and H. Tenhunen, "A High-Performance Network Interface Architecture for NoCs Using Reorder Buffer Sharing," in Proceedings of 18th IEEE Euromicro Conference on Parallel, Distributed and Network-Based Computing (*PDP*), pp. 547-550, February 2010, Italy.

- M. Daneshtalab, M. Ebrahimi, P. Liljeberg, J. Plosila, and H. Tenhunen, "Pipeline-Based Interlayer Bus Structure for 3D Networks-on-Chip," in Proceedings of 15th International Symposium on Computer Architecture and Digital Systems (*CADS*), IEEE Press, pp. 41-47, Sept 2010, Iran.

- M. Ebrahimi, M. Daneshtalab, N. Sreejesh, P. Liljeberg, Juha Plosila, and H. Tenhunen, "Efficient Network Interface Architecture for Network-on-Chips," in Proceedings of 27th IEEE *Norchip Conference*, pp. 1-4, Nov 2009, Norway.

- M. Ebrahimi, M. Daneshtalab, P. Liljeberg, and H. Tenhunen, "An Efficient Unicast/Multicast Routing Protocol for MPSoCs," in Proceedings of 12th IEEE Euromicro Conference On Digital System Design (*DSD*), pp. 203-206, August 2009, Greece.

- M. Ebrahimi, M. Daneshtalab, S. Mohammadi, Juha Plosila, and H. Tenhunen, "An Efficient Dynamic Multicast Routing Protocol for Distributing Traffic in NOCs," in Proceedings of 12th IEEE/ACM Design, Automation, and Test in Europe (*DATE*), pp. 1064-1069, April 2009, France.

- P. Lotfi-Kamran, M. Daneshtalab, Z. Navabi, and C. Lucas, "BARP- A Dynamic Routing Protocol for Balanced Distribution of Traffic in NoCs to Avoid Congestion," in Proceedings of 11th ACM/IEEE Design, Automation, and Test in Europe Conference (*DATE*), pp. 1408-1413, Mar 2008, Germany.

- M. Daneshtalab, A. Pedram, M. H. Neishaburi, M. Riazati, A. Afzali-Kusha, and S. Mohammadi, "Distributing Congestions in NoCs through a Dynamic Routing Algorithm based on Input and Output Selections," in Proceedings of 20th IEEE International Conference on VLSI Design (*VLSID*), pp. 546-550, Jan 2007, India.

#### Workshop publications:

- M. Daneshtalab, M. Ebrahimi, P. Liljeberg, J. Plosila, and H. Tenhunen, "An Efficient Topology for 3D Stacked Architectures," 3D Integration Workshop, The Design, Automation, and Test in Europe conference (*DATE*), March 2011, France.

- M. Daneshtalab, M. Ebrahimi, P. Liljeberg, J. Plosila, and H. Tenhunen, "High-Performance TSV Architecture for 3-D ICs," in Proceedings of 9<sup>th</sup> IEEE International Symposium on VLSI (*ISVLSI*), PhD-Forum, pp. 467-468, May 2010, Greece.

- M. Daneshtalab, M. Ebrahimi, P. Liljeberg, Juha Plosila, and H. Tenhunen, "A Novel Interlayer Bus Architecture for Three-Dimensional Network-on-Chips," 3D Integration Workshop, The Design, Automation, and Test in Europe (*DATE*) conference, March 2010, Germany.

# **CONTENTS**

| 1 | INTR    | ODUCTION                                     | 1  |

|---|---------|----------------------------------------------|----|

|   | 1.1 The | ADVANTAGES OF ON-CHIP NETWORKS               | 2  |

|   | 1.1.1   | Energy Efficiency                            |    |

|   | 1.1.2   | <del></del>                                  |    |

|   | 1.1.3   | Reusability                                  |    |

|   | 1.1.4   | Scalability                                  |    |

|   | 1.1.5   | Flexibility                                  | 4  |

|   | 1.2 TH  | REE-DIMENSIONAL ICS                          | 4  |

|   | 1.2.1   | 3D IC Technology Overview                    | 5  |

|   | 1.2.2   | 02 110 0                                     |    |

|   | 1.3 AD  | APTIVE ON-CHIP NETWORK                       | 6  |

|   | 1.4 Thi | SIS CONTRIBUTIONS                            | 7  |

|   | 1.5 Thi | SIS ORGANIZATION                             | 8  |

|   |         |                                              |    |

| 2 | ON-C    | HIP NETWORKS                                 | 9  |

|   | 2.1 NET | WORK TOPOLOGY                                | 9  |

|   |         | TCHING MECHANISM                             |    |

|   | 2.2.1   | Store-and-Forward                            |    |

|   | 2.2.2   | Virtual Cut-Through                          | 12 |

|   | 2.2.3   | Wormhole                                     | 12 |

|   | 2.3 VIR | TUAL CHANNELS                                | 13 |

|   | 2.4 Ou  | TPUT SCHEDULING                              | 14 |

|   | 2.5 Ro  | JTING ALGORITHM                              |    |

|   | 2.5.1   | 8                                            |    |

|   | 2.5.2   | Deterministic versus Adaptive Routing        |    |

|   | 2.5.3   | Minimal versus Non-Minimal Routing           |    |

|   | 2.5.4   | Unicast and Multicast Routing Protocols      |    |

|   | 2.5.5   | Deadlock and Livelock                        |    |

|   | 2.5.6   | Turn Model Routing                           |    |

|   |         | WORK-ON-CHIP ARCHITECTURE                    |    |

|   | 2.7 Sun | MMARY                                        | 19 |

| 2 | 475.43  | OTIVE DOLUTING BROTOGOLG IN NETWORKS ON CHAP | 21 |

| 3 |         | PTIVE ROUTING PROTOCOLS IN NETWORKS-ON-CHIP  | 21 |

|   | 2 1 HM  | CAST DOLUTING DROTOGOLS                      | 21 |

|   | 3.1.1   | XY Routing Scheme                                     | 21 |

|---|---------|-------------------------------------------------------|----|

|   | 3.1.2   | DyAD Routing Scheme                                   | 22 |

|   | 3.1.3   | DyXY Routing Scheme                                   | 24 |

|   | 3.1.4   | EDXY Routing Scheme                                   | 25 |

|   | 3.1.5   | Experimental Results                                  | 28 |

|   | 3.2 Mu  | LTICAST ROUTING PROTOCOLS                             | 34 |

|   | 3.2.1   | Unicast-based Multicast Routing                       |    |

|   | 3.2.2   | Tree-based Multicast Routing                          |    |

|   | 3.2.3   | Hamiltonian Path-based Multicast Routing Algorithm    |    |

|   | 3.2.4   | Hamiltonian Adaptive Multicast Unicast Method (HAMUM) | 41 |

|   | 3.2.5   | Hardware Implementation                               |    |

|   | 3.2.6   | Experimental Results                                  |    |

|   | 3.3 Sun | 1MARY                                                 | 58 |

| 4 | ADAI    | PTIVE ON-CHIP ROUTER ARCHITECTURE                     | 61 |

|   |         | APTIVE INPUT-SELECTION AND OUTPUT-SELECTION METHODS   |    |

|   | 4.2 MIN | IIMAL AND NON-MINIMAL IMPLEMENTATIONS OF HAMUM        |    |

|   | 4.2.1   | Deadlock Avoidance                                    |    |

|   |         | AIOS ROUTER ARCHITECTURE                              |    |

|   | 4.3.1   | $\mathcal{C}$                                         |    |

|   | 4.3.2   |                                                       |    |

|   |         | PERIMENTAL RESULTS                                    |    |

|   | 4.4.1   |                                                       |    |

|   |         | Power Dissipation                                     |    |

|   | 4.4.3   | 11414,,414                                            |    |

|   | 4.5 SUN | MARY                                                  | 77 |

| 5 | ADAI    | PTIVE NETWORK INTERFACE ARCHITECTURE                  | 79 |

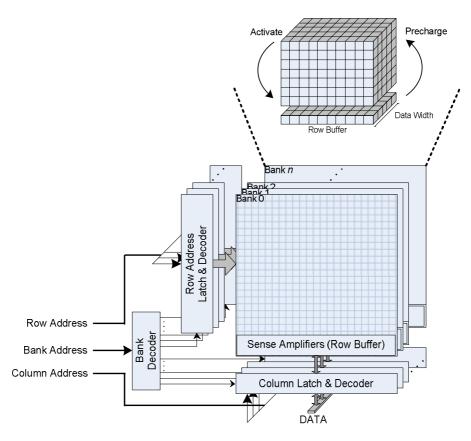

|   | 5.1 DR  | AM Structure                                          |    |

|   | 5.1.1   | Memory Access Scheduling                              |    |

|   |         | ATED WORK                                             |    |

|   | 5.3 PRC | POSED NETWORK INTERFACE ARCHITECTURE                  |    |

|   | 5.3.1   | Master-side Network Interface                         |    |

|   | 5.3.2   | Slave-side Network Interface                          |    |

|   | 5.3.3   | <i>J</i>                                              |    |

|   |         | ORITY-BASED ROUTER ARCHITECTURE                       |    |

|   | 5.4.1   | The Proposed Priority-based Router                    |    |

|   |         | DER SENSITIVE MEMORY SCHEDULER                        |    |

|   |         | PERIMENTAL RESULTS                                    |    |

|   | 5.6.1   | ,                                                     |    |

|   | 5.6.2   | Performance Evaluation                                | QQ |

| 5.6.3 Hardware Overhead                        | 102 |

|------------------------------------------------|-----|

| 5.7 Summary                                    | 102 |

|                                                |     |

| 6 THREE-DIMENSIONAL NETWORKS-ON-CHIP           | 105 |

| 6.1 3D NoC Architecture                        | 106 |

| 6.2 CONSTRAINT ON THE NUMBER OF TSVS           | 107 |

| 6.3 RELATED WORK                               | 108 |

| 6.4 PIPELINE BUS ARCHITECTURE                  | 109 |

| 6.4.1 Transfer Stage Micro-Architecture        | 111 |

| 6.4.2 Weight-based Arbitration                 | 112 |

| 6.4.3 Non-blocking Scheme                      | 113 |

| 6.4.4 Synchronizing FIFO                       | 114 |

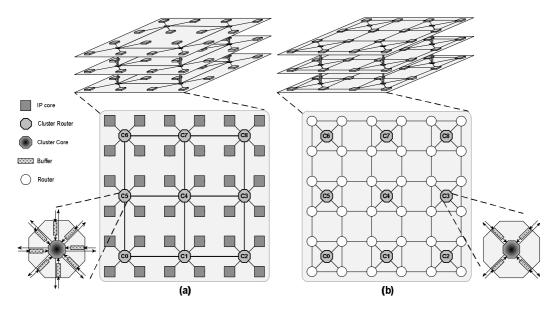

| 6.5 Cluster Architectures                      | 116 |

| 6.5.1 CIT (Concentrated Inter-layer Topology)  |     |

| 6.5.2 CMIT (Cluster Mesh Inter-layer Topology) | 117 |

| 6.5.3 Routing Algorithm                        | 118 |

| 6.6 EXPERIMENTAL RESULTS                       | 119 |

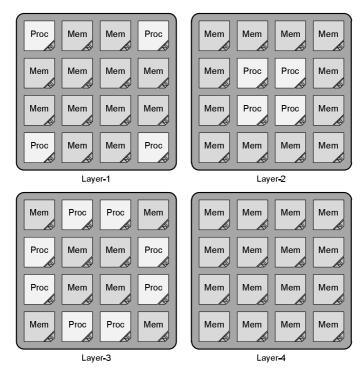

| 6.6.1 System Configuration                     | 120 |

| 6.6.2 Performance Comparison                   |     |

| 6.6.3 Power Analysis                           |     |

| 6.6.4 Physical Analysis                        |     |

| 6.7 Summary                                    | 127 |

| 7 CONCLUSION                                   | 129 |

| 7.1 Thesis Contributions                       | 120 |

| 7.1 THESIS CONTRIBUTIONS                       |     |

| 7.2 PUTURE DIRECTIONS                          | 130 |

| REFERENCES                                     | 133 |

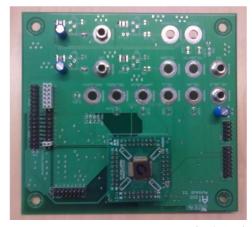

| A HARDWARE PROTOTYPING                         | 142 |

# **List of Figures**

| 1-1. Tile-based 2D-Mesh topology.                                                                                                                                     | 2      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 1-2. (a) Homogeneous and (b) Heterogeneous 3-D Network-on-Chip structures using                                                                                       | ;      |

| Through Silicon Vias (TSVs) technology to connect stacked layers vertically                                                                                           | 5      |

| 2-1. Network topologies of Shared-bus, Ring, Crossbar, Mesh, Torus, and Butterfly                                                                                     | 11     |

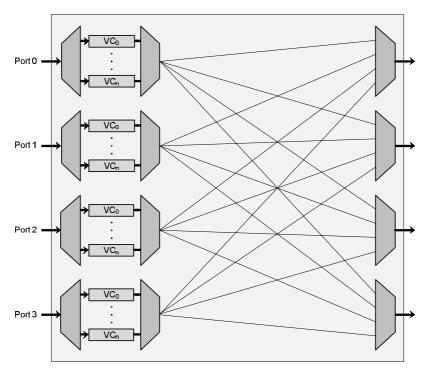

| 2-2. A typical router using VCs.                                                                                                                                      |        |

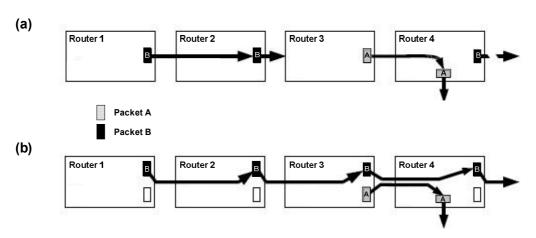

| 2-3. Using VC for avoiding deadlock.                                                                                                                                  |        |

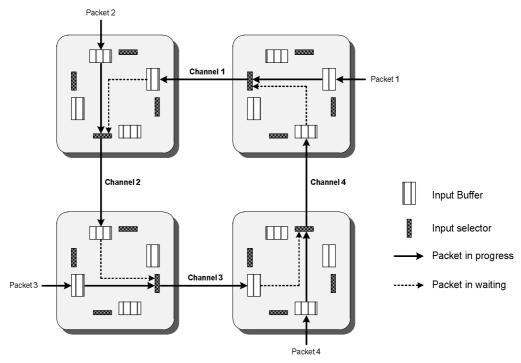

| 2-4. Deadlock scenario with four packets [68]                                                                                                                         |        |

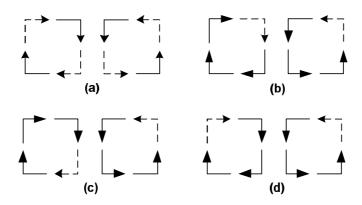

| 2-5. All possible turns in (a) XY routing (b) Negative-First (c) West-First (d) North-I (The solid lines indicate the allowable turns and the dash lines indicate the | Last   |

|                                                                                                                                                                       | 17     |

| 2-6. The Odd-Even turn model rules: (a) prohibited turns in even columns (b) prohibited                                                                               |        |

| turns in odd columns.                                                                                                                                                 |        |

| 2-7. Tile-based 2D-Mesh topology.                                                                                                                                     | 19     |

| 3-1. Illustration of different routing schemes.                                                                                                                       | 22     |

| 3-2. Structure of the XY router.                                                                                                                                      |        |

| 3-3. Structure of the DyAD router.                                                                                                                                    |        |

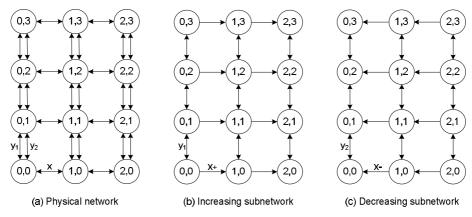

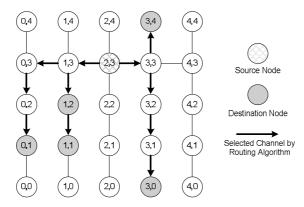

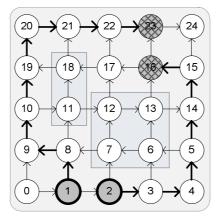

| 3-4. (a) A 3×4 mesh physical network and the corresponding (b) increasing and (c)                                                                                     | 20     |

| decreasing subnetworks                                                                                                                                                | 24     |

| 3-5. A simple NoC with mesh structure.                                                                                                                                |        |

| 3-6. An EDXY router implementation.                                                                                                                                   |        |

| 3-7. EDXY routing algorithm.                                                                                                                                          |        |

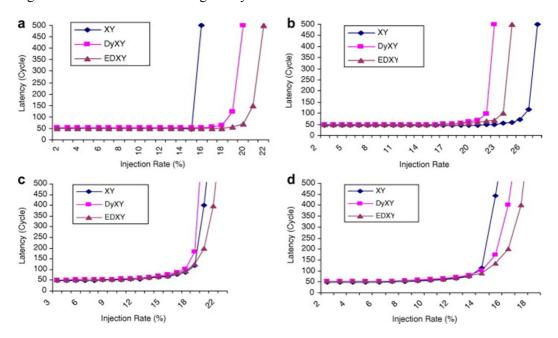

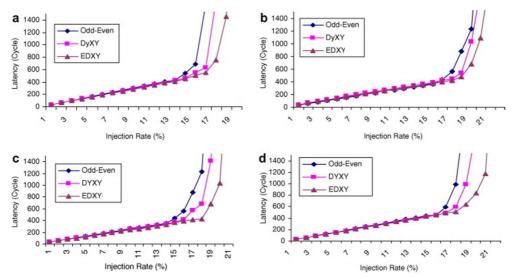

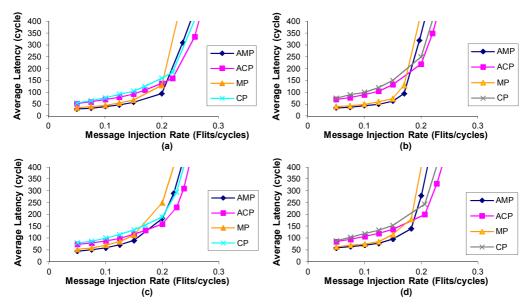

| 3-8. Latency vs. packet injection rate for EDXY, DyXY, and XY for a $7 \times 7$ 2D mesh                                                                              |        |

| flit packets with virtual channel. (a) transpose traffic, (b) uniform random traffic                                                                                  |        |

| hotspot 5%, and (d) hotspot 10%.                                                                                                                                      |        |

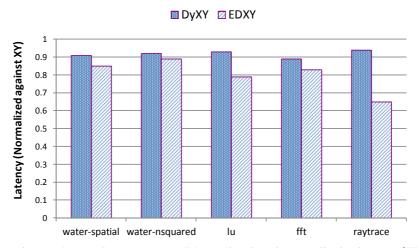

| 3-9. Average latency across SPLASH-2 benchmarks normalized to latency of XY                                                                                           |        |

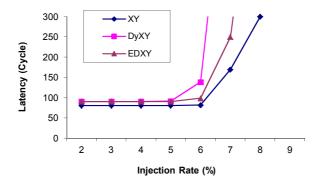

| 3-10. Latency vs. packet injection rate for $15 \times 15$ mesh with virtual channel under                                                                            |        |

| transpose traffic profile using 9-flit packets.                                                                                                                       | 32     |

| 3-11. Average latency vs. packet injection rate on a $7 \times 7$ 2D mesh for 15-flit packets                                                                         |        |

| virtual channel. (a) transpose traffic, (b) uniform random traffic, (c) hotspot 5%,                                                                                   | , and  |

| (d) hotspot 10%.                                                                                                                                                      | 33     |

| 3-12. Latency vs. packet injection rate on a $5 \times 5$ 2D mesh without virtual channel. (a                                                                         | a)     |

| transpose traffic, (b) uniform random traffic, (c) hotspot 5%, and (d) hotspot 109                                                                                    |        |

| 3-13. Example of tree-based multicast routing in 5×5 2D-mesh                                                                                                          | 35     |

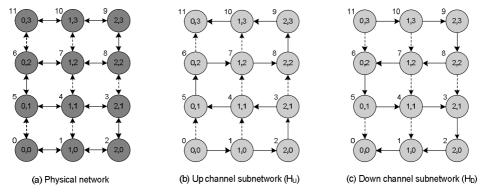

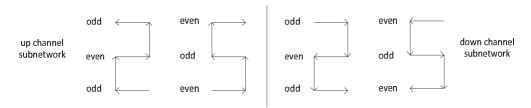

| 3-14. A 3×4 mesh physical network with the label assignment and the corresponding                                                                                     | (b) up |

| channel and (c) down channel networks. The solid lines indicate the Hamiltonian                                                                                       | n path |

|      | and dashed lines indicate the links that could be used to reduce the path length in routing                                                                             | 6 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

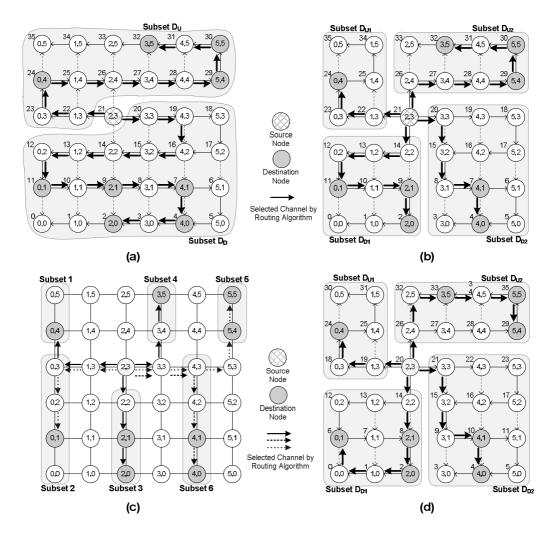

| 3-15 | Examples of (a) Dual-path (DP), (b) Multi-path (MP), (c) Column-Path (CP), and (d) Low-Distance (LD) multicast routing from (2, 3). The unused links are not indicated. |   |

| 3-17 | . Message header construction for Low Distance (LD) multicast routing 4 . The pseudo code of HAMUM                                                                      |   |

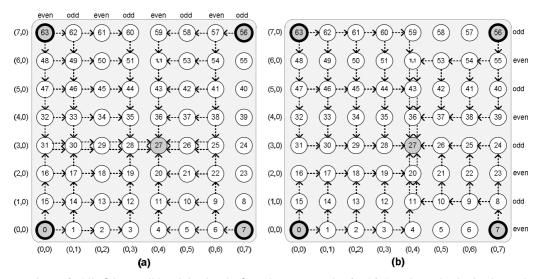

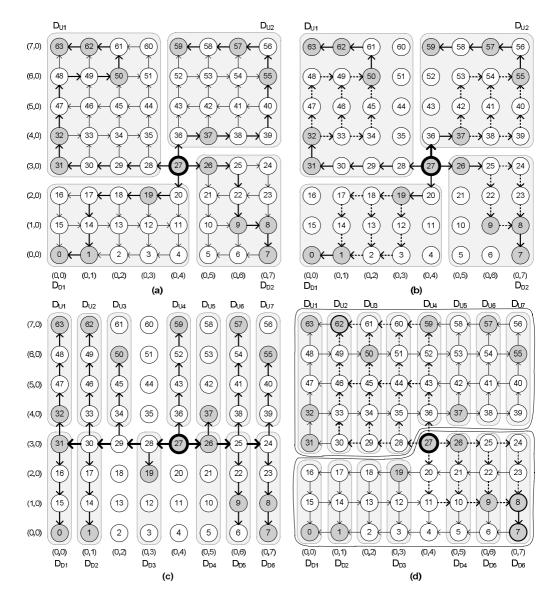

| 3-18 | . All of the possible minimal paths from the source nodes 63, 56, 7, and 0 to the destination node 27 in (a) the Odd-Even model, and (b) the unicast aspect of HAMUM    | 3 |

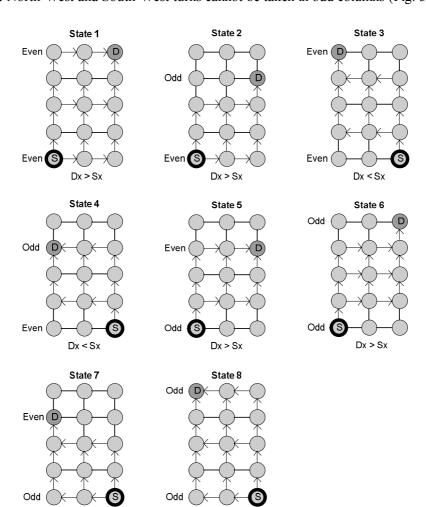

| 3-19 | Eight different location states in the up channel subnetwork                                                                                                            |   |

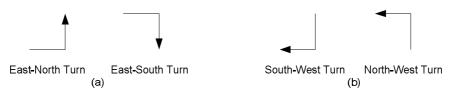

|      | The Odd-Even turn model rules: (a) prohibited turns in even columns (b) prohibited turns in odd columns                                                                 |   |

| 3-21 | . (a) Multi-Path (MP), (b) Adaptive Multi-Path (AMP), (c) Column-Path (CP), and                                                                                         | • |

|      | Adaptive Column-Path (ACP) routing algorithms. 4                                                                                                                        |   |

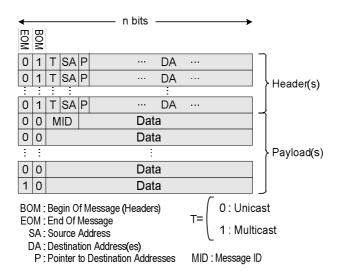

|      | . Multicast message format for the proposed technique                                                                                                                   |   |

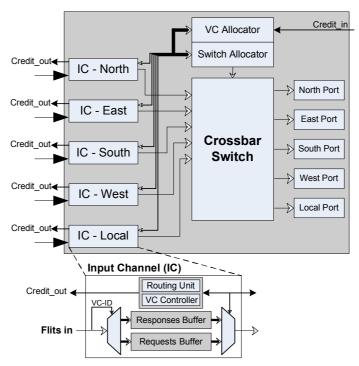

|      | . The proposed router structure                                                                                                                                         |   |

|      | Deadlock due to the delivery channel contention [81].                                                                                                                   | U |

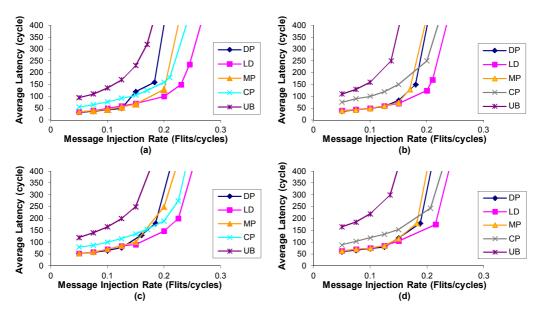

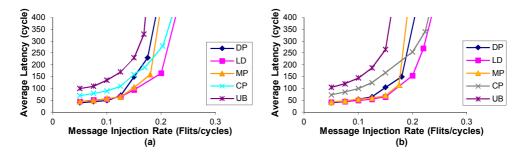

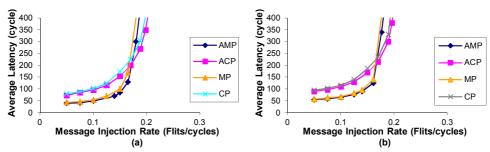

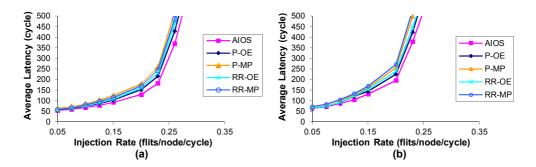

| 3-25 | Performance evaluation of LD under different loads in 8×8 2D-mesh with (a) 10                                                                                           | _ |

|      | destinations, (b) 25 destinations and in 16×16 2D-mesh with (c) 10 destinations, (d) 2                                                                                  |   |

| 2.26 | destinations under multicast traffic model                                                                                                                              | 2 |

| 3-26 | . Performance evaluation of HAMUM under different loads in 8×8 2D-mesh with (a) 10 destinations, (b) 25 destinations and in 16×16 2D-mesh with (c) 10 destinations, (d) | ) |

|      | 25 destinations under multicast traffic model.                                                                                                                          |   |

| 3-27 | Performance evaluation of LD under different loads in 8×8 2D-mesh with (a) 10                                                                                           | _ |

|      | destinations, (b) 25 destinations under mixed traffic (20% multicast and 80% unicast)                                                                                   |   |

|      | while unicast traffic is based on the uniform traffic model                                                                                                             | 4 |

| 3-28 | . Performance evaluation of HAMUM under different loads in 8×8 2D-mesh with (a)                                                                                         |   |

|      | 10 destinations, (b) 25 destinations under mixed traffic (20% multicast and 80%                                                                                         |   |

|      | unicast) while unicast traffic is based on the uniform traffic model                                                                                                    | 4 |

| 3-29 | . Performance evaluation of LD under different loads in 8×8 2D-mesh with (a) 10                                                                                         |   |

|      | destinations, (b) 25 destinations under mixed traffic (20% multicast and 80% unicast).                                                                                  |   |

|      | Unicast traffic is based on the hotspot traffic model with a single hotspot node (4, 4).                                                                                |   |

|      | The hotspot percentage is 10%.                                                                                                                                          | 4 |

| 3-30 | . Performance evaluation of HAMUM under different loads in 8×8 2D-mesh with (a)                                                                                         |   |

|      | 10 destinations, (b) 25 destinations under mixed traffic (20% multicast and 80%                                                                                         |   |

|      | unicast). Unicast traffic is based on the hotspot traffic model with a single hotspot                                                                                   |   |

|      | node (4, 4). The hotspot percentage is 10%                                                                                                                              | 5 |

| 3-31 | . Performance under different application benchmarks for multi-path (left) and column                                                                                   |   |

|      | path (right) routing algorithms. 5                                                                                                                                      |   |

|      |                                                                                                                                                                         |   |

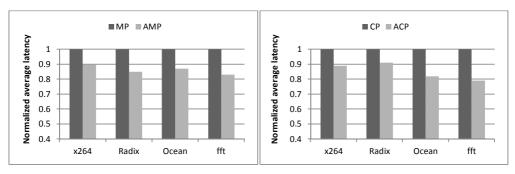

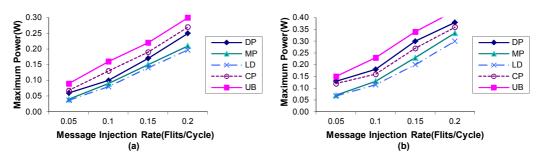

| 3-32. Average power dissipation of the proposed, the DP, the MP and the CP algorithms 16×16 2D-mesh with (a) 10 destinations and (b) 25 destinations under multicast |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| traffic.                                                                                                                                                             |     |

| 3-33. Maximum power dissipation of the proposed, the DP, the MP and the CP algorithm                                                                                 |     |

| in 16×16 2D-mesh with (a) 10 destinations and (b) 25 destinations under multicast                                                                                    |     |

| traffic.                                                                                                                                                             |     |

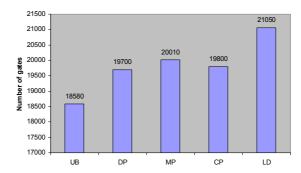

| 3-34. Area cost of routers for implementing different multicast routing algorithms                                                                                   | 58  |

| 4.1. The provide VIIDL and a functified HAMLIM including the non-minimal routing                                                                                     | 62  |

| <ul><li>4-1. The pseudo VHDL code of modified HAMUM including the non-minimal routing.</li><li>4-2. An example of modified HAMUM.</li></ul>                          |     |

| 4-3. All possible turns of HAMUM and modified HAMUM.                                                                                                                 | 04  |

|                                                                                                                                                                      |     |

| 4-4. The proposed routing structure.                                                                                                                                 |     |

| 4-5. Congestion detection circuit for the input buffer                                                                                                               |     |

| 4-6. Congestion level computation and transmission scheme.                                                                                                           |     |

| 4-7. Routing unit circuit.                                                                                                                                           |     |

| 4-8. The procedure of selecting the suitable output port                                                                                                             |     |

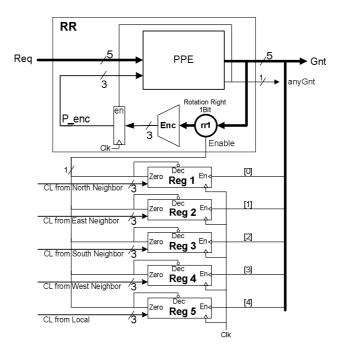

| 4-9. Block diagram of a round-robin arbiter.                                                                                                                         |     |

| 4-10. Block diagram of a weighted round robin arbiter.                                                                                                               | / 1 |

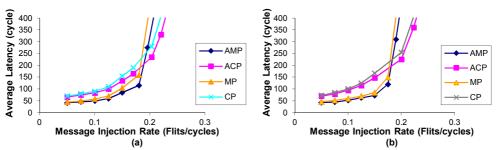

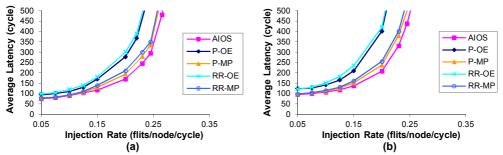

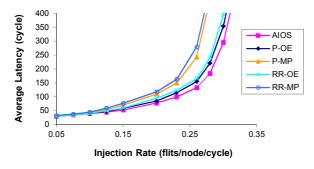

| 4-11. Performance results in 8×8 2D-mesh under multicast traffic profile with (a) 10                                                                                 | 70  |

| destinations, (b) 20 destinations.                                                                                                                                   |     |

| 4-12. Performance with different loads in 8×8 2D-mesh under mixed traffic (20% multic                                                                                |     |

| and 80% unicast). Unicast traffic in (a) is based on the uniform pattern and in (b) is                                                                               |     |

| based on the hotspot pattern with h=10%                                                                                                                              | 74  |

| 4-13. Performance with different loads in 8×8 2D-mesh under unicast traffic: (a) the                                                                                 |     |

| uniform pattern and (b) the hotspot pattern.                                                                                                                         | 74  |

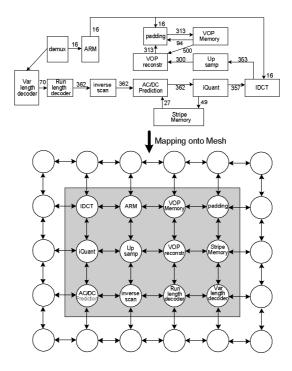

| 4-14. The VOPD block diagram, with communication BW annotated (in MB/s) and its                                                                                      |     |

| mapping onto mesh topology.                                                                                                                                          |     |

| 4-15. The performance of different algorithms under VOPD traffic model.                                                                                              |     |

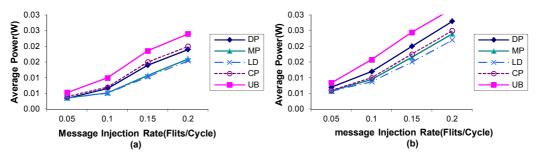

| 4-16. (a) Average and (b) Maximum power dissipation results in 8×8 2D-mesh under m                                                                                   |     |

| traffic profile.                                                                                                                                                     |     |

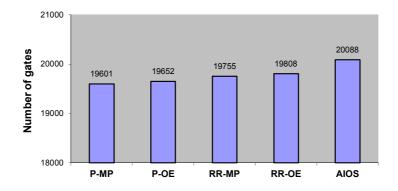

| 4-17. Area cost of routers for implementing different input-output selections                                                                                        | 77  |

| 5 1 High level structure of an CDD AM                                                                                                                                | 0.1 |

| 5-1. High-level structure of an SDRAM.                                                                                                                               |     |

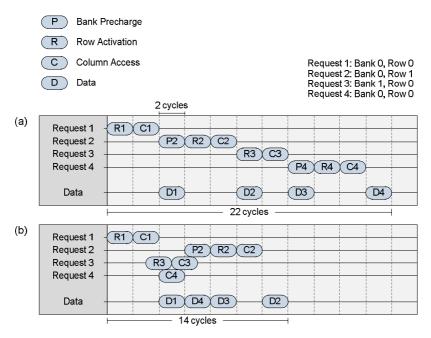

| 5-2. Memory access scheduling of four memory requests with (a) in-order and (b) with o                                                                               |     |

| of-order access scheduling.                                                                                                                                          |     |

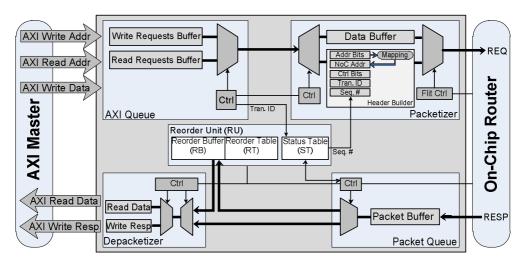

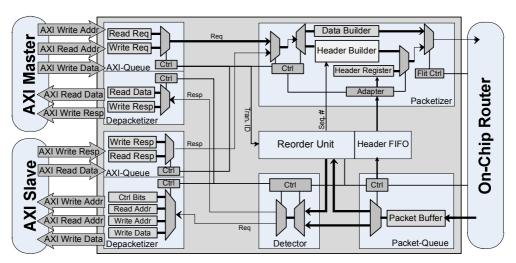

| 5-3. Master-side network interface architecture.                                                                                                                     |     |

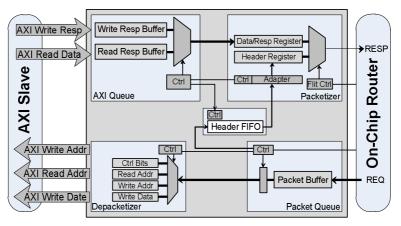

| 5-4. Slave-side network interface architecture.                                                                                                                      |     |

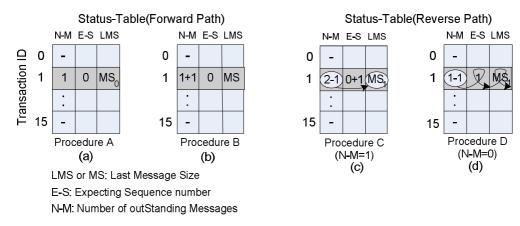

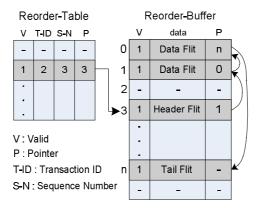

| 5-5. Status-Table of the reorder unit.                                                                                                                               |     |

| 5-6. Dynamic buffer allocation.                                                                                                                                      |     |

| 5-7. Hybrid network interface architecture.                                                                                                                          |     |

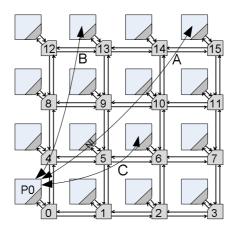

| 5-8. 4×4 NoC where master core 0 sends requests A, B and C to memories 6, 13 and 15                                                                                  |     |

| respectively.                                                                                                                                                        | 91  |

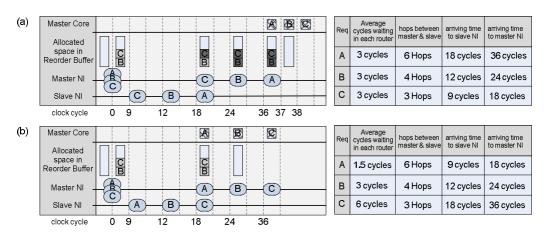

| 5-9. Comparing (a) round-robin and (b) priority-based arbitration schemes in serializing packets.                                                                            |            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 5-10. The router architecture.                                                                                                                                               |            |

| 5-11. Pseudo VHDL code of the priority-based router.                                                                                                                         |            |

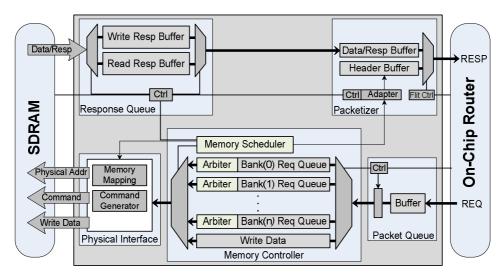

| 5-12. The proposed memory controller integrated in the slave-side network interface.                                                                                         |            |

| 5-13. Pseudo VHDL code of the arbiter in the memory controller.                                                                                                              |            |

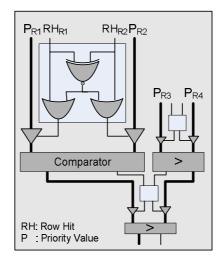

| 5-14. Request selector circuit.                                                                                                                                              |            |

| 5-15. The layout of the system configuration A.                                                                                                                              |            |

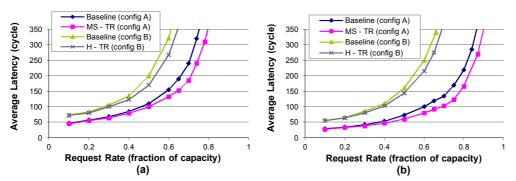

| 5-16. Performance evaluation of both configurations under (a) uniform and (b) non-uni traffic models.                                                                        | form<br>99 |

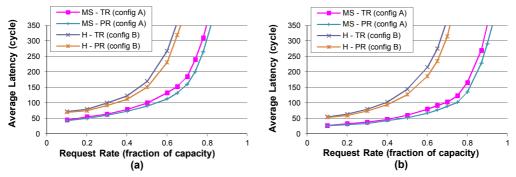

| 5-17. Performance impact of using the priority-based router under the (a) uniform and (non-uniform traffic models.                                                           |            |

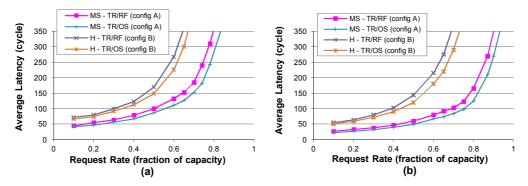

| 5-18. Performance impact of using the order sensitive memory controller under the (a) uniform and (b) non-uniform traffic models.                                            |            |

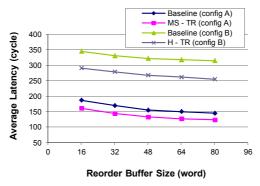

| 5-19. Effect of reorder buffer size on the performance under the uniform traffic model.                                                                                      | 101        |

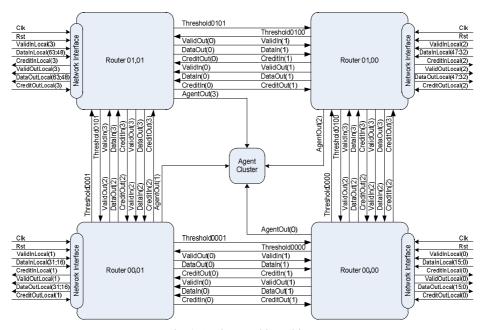

| 6-1. Mesh-based NoC architectures: (a) 3D-symmetric NoC (b) 3D NoC-Bus Hybrid structures.                                                                                    |            |

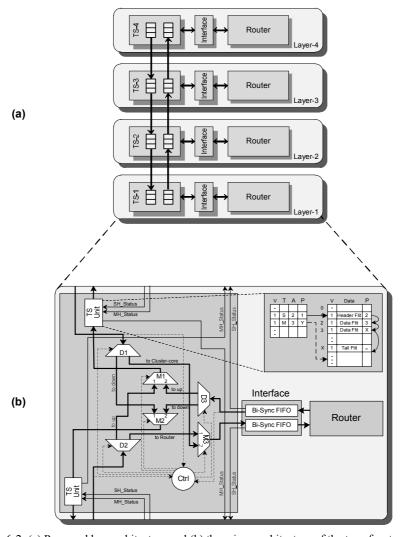

| 6-2. (a) Proposed bus architecture and (b) the micro-architecture of the transfer stage. 6-3. Pseudo VHDL code of the weight-based arbitration for multiplexers: M1, M2, and | d M3       |

|                                                                                                                                                                              |            |

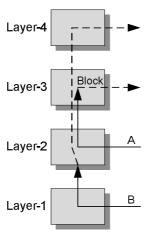

| 6-4. A blocking situation.                                                                                                                                                   |            |

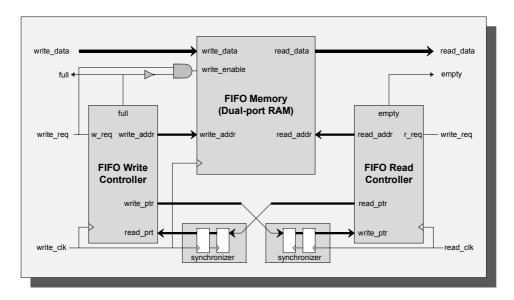

| 6-5. Bi-Sync FIFO structure.                                                                                                                                                 |            |

| 6-6. Clustering approaches: (a) CIT and (b) CMIT.                                                                                                                            |            |

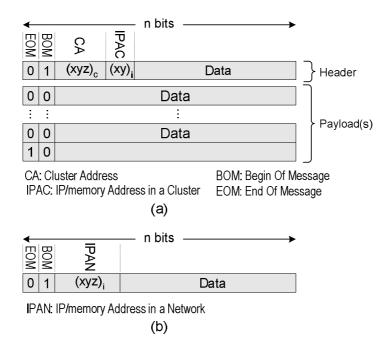

| 6-7. (a) The packet format in CIT and (b) the header format in CMIT.                                                                                                         |            |

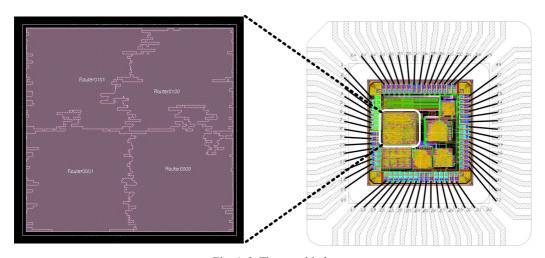

| 6-8. 4×4×4 stacked mesh layout.                                                                                                                                              |            |

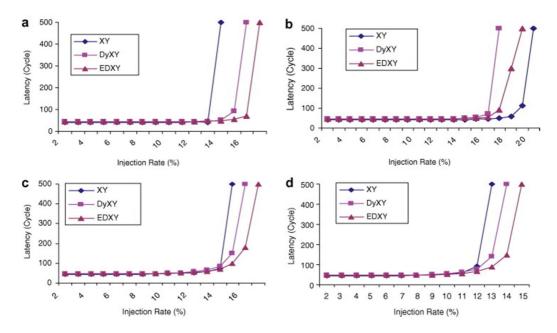

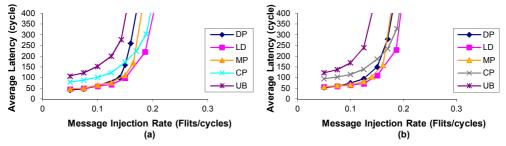

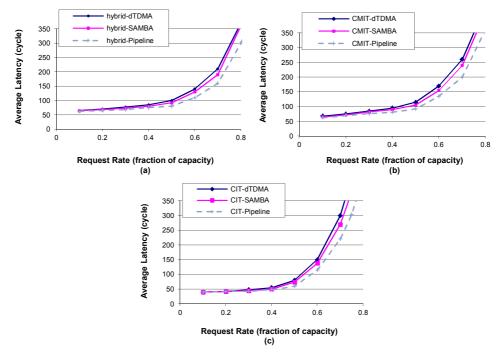

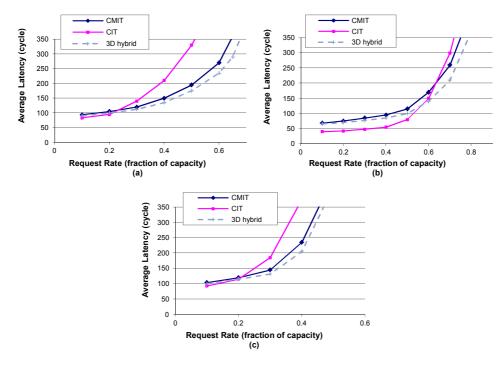

| 6-9. Performance impact of using the presented bus in (a) hybrid, (b) CMIT, and (c) C                                                                                        |            |

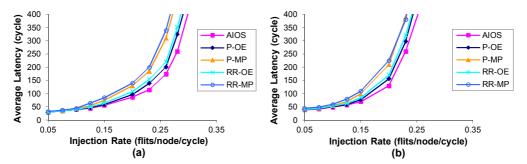

| networks under uniform traffic profile.                                                                                                                                      | 121        |

| 6-10. Performance impact of using the presented bus in (a) hybrid, (b) CMIT, and (c)                                                                                         |            |

| networks under non-uniform traffic profile.                                                                                                                                  | 122        |

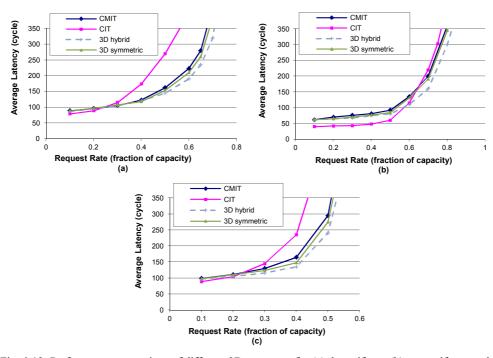

| 6-11. Performance comparison of different 3D structures for (a) the uniform, (b) non-                                                                                        | 100        |

| uniform, and (c) hotspot traffic profiles using dTDMA.                                                                                                                       | 123        |

| 6-12. Performance comparison of different 3D structures for (a) the uniform, (b) non-                                                                                        | 104        |

| uniform, and (c) hotspot traffic profiles using the presented bus.                                                                                                           |            |

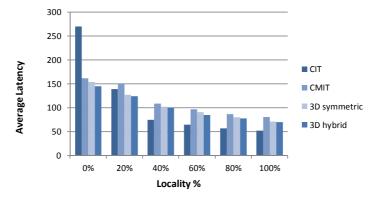

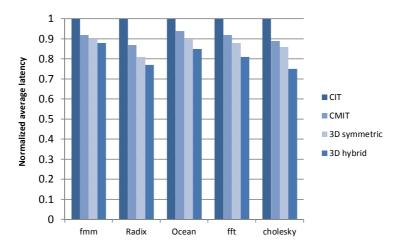

| 6-13. Performance impact of topologies using presented bus with different local loads. 6-14. Performance for application traces normalized to CIT.                           |            |

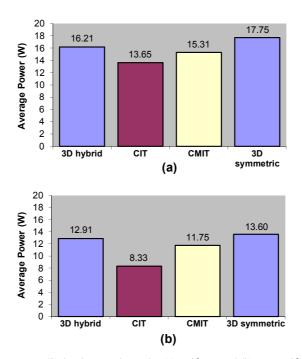

| 6-15. Average power dissipation results under (a) uniform and (b) non-uniform traffic                                                                                        | 123        |

|                                                                                                                                                                              | 126        |

| profiles.                                                                                                                                                                    | 140        |

# **List of Tables**

| 3-1.         | Baseline network configuration and variation.                                                                  | 28  |

|--------------|----------------------------------------------------------------------------------------------------------------|-----|

| 3-2.         | System configuration parameters.                                                                               | 30  |

| 3-3.         | Area comparison of XY, DyXY, and EDXY.                                                                         | 34  |

|              | Power consumption of DyXY and EDXY routing under the uniform traffic profile (mW).                             |     |

| 3-5.         | Eight different location states of the source and destination nodes.                                           |     |

|              | Comparative average power dissipation of LD with other algorithms in 16×16 2D-                                 |     |

|              | mesh.                                                                                                          | 57  |

| 3-7.         | Comparative maximum power dissipation of LD with other algorithms in 16×16 2D-                                 | -   |

|              | mesh.                                                                                                          | 57  |

| 3-8.         | Comparative average power dissipation of the adaptive schemes using HAMUM model with the conventional schemes. | 57  |

| <b>3-</b> 9. | Comparative maximum power dissipation of the adaptive schemes using HAMUM                                      |     |

|              | model with the conventional schemes.                                                                           | 57  |

| <b>4-</b> 1. | Structure of other four routers.                                                                               | 72  |

| 5-1.         | Hardware implementation details.                                                                               | .02 |

| 6-1.         | Description of Bi-Sync FIFO signals                                                                            | 15  |

| 6-2.         | Number of routers, cluster routers and vertical channels of the described topologies i                         | n   |

|              | a (4×4×3) 3D architecture                                                                                      | .17 |

## **List of Abbreviations**

**3D-IC** Three Dimensional Integrated Circuit

**ACP** Adaptive Column-Path

AIOS Adaptive Input-Output Selection

AMBA Advanced Microcontroller Bus Architecture

**AMP** Adaptive Multi-Path

**AXI** Advanced eXtensible Interface

B2B Back-to-Back BOM Begin Of Message

CAIS Contention-Aware Input Selection

CAM Content Addressable Memory

CARS Contention Aware Routing Selection

**CF** Congestion Flag

CIT Concentrated Inter-layer Topology

CMIT Clustered Mesh Inter-layer Topology

CL Congestion Level

**CMOS** Complementary Metal–Oxide–Semiconductor

**CMP** Chip-Multiprocessor

CP Column-Path

CS Congestion Status

DA Destination Address

DoA Degree of Adaptiveness

DOR Dimension Order Routing

**DP** Dual-Path

**DRAM** Dynamic Random Access Memory **dTDMA** Dynamic Time Division Multiple Access

**DTL** Device Transaction Level

**DU** Depacketizer Unit

**DyAD** Dynamic Adaptive Deterministic

**DvXY** Dynamic XY

ECC Error Correcting Codes

EDXY Enhanced Dynamic XY

EOM End Of Message

F2B Face-to-Back

F2F Face-to-Face

**FCFS** First Come First Service

**FIFO** First In First Out

**FLIT** FLow control digIT

**FPGA** Field Programmable Gate Array

GALS Globally Asynchronous Locally Synchronous

GEMS General Execution-driven Multiprocessor Simulator

HAMUM Hamiltonian Adaptive Multicast Unicast Method

HoL Head of Line blocking IP Intellectual Property

ITRS International Technology Roadmap for Semiconductors

**LD** Low Distance

MESI Modified Exclusive Shared Invalid

MH Multiple Hop MID Message IDentifier

MLBS Multi-Layer Buried Structures

MOESI Modified Owned Exclusive Shared Invalid

**MP** Multi-Path

MPSoC Multi-Processor System-on-Chip

NF Negative-First NI Network Interface

NMOS N-Channel Metal-Oxide-Semiconductor

NL North-Last

NoC Network-on-Chip OCP Open Core Protocol

OE Odd-Even Order Sensitive

**PARSEC** Princeton Application Repository for Shared-Memory Computers

**PB** Path-Based

PCI Peripheral Component Interconnect

**PE** Processing Element

**PPE** Programmable Priority Encoder

PR Priority-based Router

PU Packetizer Unit

QoS Quality-of-Service

RAM Random Access Memory

**RF** Row First

ROM Read Only Memory RR Round-Robin

**RTL** Register Transfer Level

RU Reorder Unit SA Source Address

SAMBA Single Arbitration Multiple Bus Accesses

SDRAM Synchronous Dynamic Random Access Memory

SH Single Hop

SIA Semiconductor Industry Association SNUCA Static Non-Uniform Cache Architecture

**SoC** Systems-on-Chip

**SPARC** Scalable Processor ARChitecture

SPLASH Stanford Parallel Applications for Shared Memory

STL Standard Template Libraries

SV Stress Value TB Tree-Based TR Typical Router Transfer Stage TS **TSV** Through Silicon Via UB Unicast-Based VC Virtual Channels **VCT** Virtual Circuit Table

VCTM Virtual Circuit Tree Multicasting

VHDL VHSIC hardware description language

VHSIC Very-High-Speed Integrated Circuits

VLSI Very Large Scale Integration VOPD Video Object Plane Decoder

WF West-First

WRR Weighted Round Robin

# Chapter 1

# Introduction

As indicated by several researchers and the International Technology Roadmap for Semiconductors (ITRS), nanometer Systems-on-Chip (SoCs) will most likely not have an economic yield if all transistors must be functional [1][2]. Besides, it is expected that Moore's law will continue to hold for another five to fifteen years where billion gates can be integrated in a chip. This capacity will allow integration of several tens to hundred resources like processor cores, DSP cores, and interface circuits (like Blue-tooth or Ethernet adapter), FPGA blocks, analog blocks, and memory blocks (any kind such as RAM, ROM and CAM). Thereby, it is possible to integrate more than one Processing Element (PE) in a SoC, being known as Multi-Processor System-on-Chip (MPSoC). MPSoCs have been widely used in high performance embedded systems, such as web servers, network processors, and parallel media processors. They combine the advantages of data processing parallelism of multi-processors and the high level integration of SoCs. The continuously increasing number of cores for such multi-billion transistor SoCs calls for a new communication architecture as traditional bus-based architectures are inherently non-scalable, making communication a bottleneck [1][2][3].

The Network-on-Chip (NoC) architecture paradigm, based on a modular packet-switched mechanism, can address many of the on-chip communication design issues such as performance limitations of long interconnects, and integration of high number of PE on a chip [1][2][3][4][5]. Notable examples of this architecture include Intel's 80-core Teraflops Research Chip [6] and Tilera's TILE64 [7].

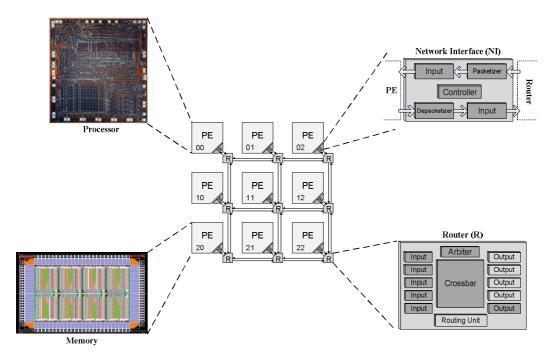

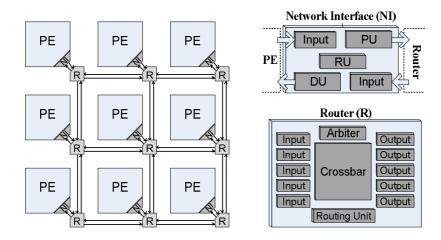

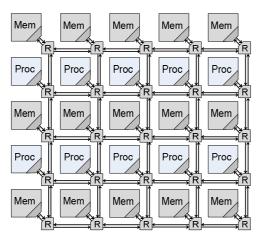

A tiled-based 2D-mesh NoC based system, where one or more cores and other resources are encapsulated into a tile, is shown in Fig. 1-1. It consists of Routers (R), PE, and Network Interfaces (NI). PEs may be intellectual property (IP) blocks or embedded memories. Each PE is connected to the corresponding router port using the network interface. This enables to use packets for transferring information between PEs without requiring dedicated wirings for point to point connection. In brief, NoCs not only offer a scalable performance needed by systems which grow with each new generation [1][2], but also allow to mitigate the energy consumption by avoiding the use of long global wires. Since all links in the NoC can operate simultaneously on different data packets, a high level

of parallelism is making it attractive for replacing previous communication architectures like dedicated point-to-point signal wires, shared buses, or segmented buses with bridges. Furthermore, NoCs are reusable templates and aid to reduce the so called design productivity gap. Finally, none of the current on-chip interconnect approaches (buses and dedicated point-to-point channels) will meet all the requirements of future SoCs, as NoCs could potentially fulfill.

Fig. 1-1. Tile-based 2D-Mesh topology.

#### 1.1 The Advantages of On-Chip Networks

Energy efficiency, reliability, reusability, scalability, and flexibility are the most important benefits of NoC from other on-chip communication approaches.

#### 1.1.1 Energy Efficiency

According to the International Technology Roadmap for Semiconductors (ITRS) [8] and Semiconductor Industry Association (SIA) [9] roadmaps, clock frequency and number of on-chip devices are increased. That is, much tighter power budgets for all system components are required. Based on the roadmaps, as computation and storage components benefit from device scaling, the energy for global communication does not scale down. Hence, communication-energy minimization will be a growing concern in future

technologies. The on-chip networks aim to reduce this problem by scaling wires. This new model allows the decoupling of the PEs from the network. The need for global synchronization can thereby disappear. This new approach employs explicit parallelism, exhibits modularity to minimize the use of global wires, and utilizes locality for power minimization [10][11]. Furthermore, network traffic control and monitoring can help in better managing the power consumed by networked computational resources. For instance, clock speed and voltage of end nodes can be varied according to available network bandwidth. The emphasis on energy minimization creates a sleuth of novel challenges that have not been addressed by traditional high-performance network designers [10][11].

#### 1.1.2 Reliability

As the geometries of the transistors reach the physical limits of operation, it becomes increasingly difficult for the hardware components to achieve reliable operation. The variability in process manufacturing, issues of thermal hotspots and effects of various noise sources, such as power supply fluctuations, pose major challenges for the reliable operation of current and future NoC-based MPSoCs. NoCs are particularly suited for implementation of fault-tolerant techniques, due to their inherent parallelism and potential for reconfigurability. Fault-tolerant techniques can be implemented at different levels, from hardware redundancy to software-based error recovery schemes. Adaptive routing algorithms combined with error detection mechanisms show great promise in achieving fault-tolerant on-chip communication. If data is sent on an unreliable channel in packets, error detection and recovery is easier, because the effect of errors is contained by packet boundaries, and error recovery can be carried out on a packet-by-packet basis. Error correction can be achieved by using standard error correcting codes (ECC), whereas robust and fault-tolerant routing algorithms can route around faulty regions [12].

#### 1.1.3 Reusability

PEs are usually obtained from internal sources or third parties, and integrated on a single chip. These reusable PEs may include embedded processors, memory blocks, interface blocks, analog blocks, and components that handle application specific processing functions. Corresponding software components are also provided in a reusable form and may include real-time operating systems and kernels, library functions, and device drivers. That is, PEs are reusable in nature if they conform to a common interface and synchronization mechanisms with the on-chip network. Using a standard interface such as AXI [13], OCP [14], and DTL [15], in on-chip networks facilitates the employment of reusable components. In fact, employing a standard interface does not change the way PEs are developed, since they will still be developed for a certain protocol. What changes is that a public domain protocol is used and accepted by the industry as a standard, like the PCI standard for microcomputer manufacturers. Accordingly, not only the PEs reusability becomes higher but also the design time is reduced [16]. In addition, on-chip routers are generic in nature and the communication can be employed with any conforming PE.

#### 1.1.4 Scalability

NoC platform is composed of on-chip routers and communication links that are basically distributed and independent. Each PE is added into the network along with a dedicated router having a unique address or coordinate in the network. The communication exploits the packet switching scheme while there is no central arbitration mechanism of the communication platform. Therefore, the performance in this communication architecture is not constrained or degraded by the addition of PEs. This is the essential characteristic of a scalable and modular architecture [1][2][3]. Indeed, on-chip interconnection network plays an important role in providing scalability to integrate hundreds or even thousands of processing elements in a single billion-transistor chip and alleviate design productivity gap [17]. In fact, using data packets for communication, a high level of parallelism is achieved as all channels can be operated simultaneously. Thereby, on-chip network improves the scalability in comparison with previous communication structures such as shared buses or segmented buses.

#### 1.1.5 Flexibility

Utilizing common buses between the communicating resources in SoCs will not give any flexibility since the needs of the communication have to be thought of every time a design is made. However, they suffer from low scalability [1]-[5]. NoC solves their shortcomings by implementing a communication network of routers and resources. NoC is a very flexible communication infrastructure allowing the same physical link to be shared by many different connections. As future SoC platforms are expected to contain hundreds of PEs, NoC needs to support an even larger number of connections and many connections span a large number of routers. This leads the same SoC platform to be used in a wide range of different applications and thereby increases the production volume. As the same SoC platform is to be used for many different applications, the NoC must be able to support a wide range of bandwidth and Quality-of-Service (QoS) requirements. The requirements of the applications can be very different, and the NoC must therefore be very flexible.

#### 1.2 Three-Dimensional ICs

Two-dimensional (2D) chip fabrication technology is facing lots of challenges in the deep submicron regime even by utilizing NoC architectures [18][19], e.g. designing the clock-tree network for a large chip, limited floor-planning choices, increasing the wire delay and power consumption, integrating various components that are digital, analog, MEMS, RF, etc. The Three Dimensional (3D) integration has emerged as a potent solution to address these problems and the design complexity of MPSoC in 2D Integration Circuits (IC). 3D ICs reduce the interconnect delay problem by stacking vertically active silicon layers as well as offering a number of advantages over the traditional 2D chip [18][19][20][21][22]: (1) shorter global interconnects; (2) higher performance; (4) high memory bandwidth; (3) lower interconnect power consumption due to wire-length reduction; (4) higher packing

density and smaller footprint; and (5) support for the implementation of mixed-technology chips, e.g. NMOS DRAM stacking on top of CMOS processor cores. However, thermal problem is still an important challenge for 3D IC circuit design.

#### 1.2.1 3D IC Technology Overview

There are many technologies for die stacking being pursued by industry and academia. Wafer-Bonding [30][31] and Multi-Layer Buried Structures (MLBS) [32][33] are the most promising ones. The details of these processes are described in [18]. Wafer-to-wafer bonding appears to be the leading contender in industry and many recent academic studies have assumed this type of 3D stacking technology [18]-[23][34]. Wafers can be stacked either Face-to-Face (F2F) or Face-to-Back (F2B) and both have pros and cons. While the former provides the greatest layer-to-layer via density, it is suitable for two-layers; and additional layers would have to employ Back-to-Back (B2B) placement using larger and longer vias. On the other hand, Face-To-Back provides uniform scalability to an arbitrary number of layers, despite a reduced inter-layer via density [27]-[35]. Layers, stacked on top of each other, are connected via vertical interconnects tunneling through them. Wire bonding, micro-bump, contactless, and Through Silicon Via (TSV) are some of the vertical interconnect (Inter-layer communication) technologies that have been used in stacked structures [32]. The distance between wafers can range from 5µm to 50µm [22][24], which is much shorter than the wire length between cores on a tier, and the pitches of a TSV can range from 1 µm to 10 µm square [22][24]. That is, the wire delay, power consumption and chip form factor are significantly reduced [25][26][28]. Thus, the TSV interconnection has the potential to offer the greatest vertical interconnect density and is the most promising one among these vertical interconnect technologies [27]-[35]. In this thesis, we assumed the F2B method with TSV interconnects to provide more scalability when more than two layers are employed.

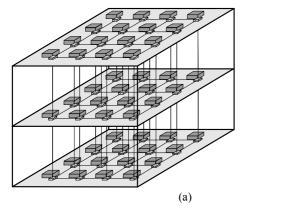

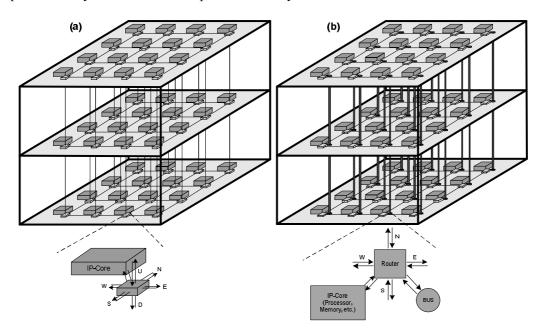

Fig. 1-2. (a) Homogeneous and (b) Heterogeneous 3-D Network-on-Chip structures using Through Silicon Vias (TSVs) technology to connect stacked layers vertically.

#### 1.2.2 3D NoC

Combining the benefits of 3D ICs and NoCs schemes provides a significant performance gain for 3D architectures. 3D NoC topologies not only create scalable networks to provide communication requirements in 3D ICs [19]-[22], but also are a crucial factor of 3D chips in terms of performance, cost, and energy consumption [19]. Various on-chip network topologies have been studied for 3D NoCs [19]-[23][25][27][29]. Mesh-based structures are popularly used in 3D systems (Fig. 1-2), because their grid-based regular structure is intuitively considered to be matched to the 2D VLSI layout for each stack layer [19][20][21][22][25]. Nevertheless, if the number of IP-cores and memories increases in each layer, more TSVs are necessitated to handle the inter-layer communication. Inasmuch as each TSV employs a pad for bonding, the area footprint of TSVs in each layer is augmented significantly [22][29].

#### 1.3 Adaptive On-Chip Network

NoC is flexible to dynamically support the communication among modules in a system with heavily varying workloads. To augment resource utilization and flexibility, the architecture of NoC needs to be integrated with novel adaptive methodologies employing resource multiplexing mechanisms at varying workloads. In the scope of this thesis, several novel adaptive schemes for the on-chip network architecture are presented to exploit all the benefits that can be obtained. Each component of on-chip network platform can be implemented adaptively to increase the utilization and performance. In order to route data packets to the non-congested area and/or give the priority to a packet passing through a congested area of the network to ease the congestion faster, respectively. Network interfaces can handle in-order delivery which is a practical approach when exploiting an adaptive routing algorithm for distributing packets through the network or when exploiting dynamic memory access scheduling in memory controller to reorder memory requests. Adaptive on-chip network interface architectures are utilized to increase the resource utilization and system performance.

In the realm of 3D NoCs, the router-based and bus-based organizations are the two dominant architectures for utilizing TSVs as inter-layer communication channel. The former suffers from poor scalability and deteriorates the performance at high injection rates, and the latter consumes more area and power. Using adaptive inter-layer communication structure not only can reduce the delay and complexity of traditional arbitration but also reduces the area overhead of TSVs, which can impact designing 3D architectures with a large number of TSVs.

#### 1.4 Thesis Contributions

Multicore designers have moved from a bus-based view of design to a network-based view to overcome several problems outlined above. NoC architectures are emerging as a scalable and modular solution to global communication within large MPSoCs. NoCs diminish the emerging wire-delay problem and address the need for substantial interconnect bandwidth by replacing shared buses with packet-switched on-chip router networks. The idea of on-chip network creates many new research opportunities. In particular, this thesis has explored the adaptive implementation of on-chip network and communication design spaces in the following directions:

- Adaptive on-chip communication routing protocols

- Adaptive on-chip router

- Adaptive network interface

- Adaptive inter-layer communication structure for 3D NoCs

This thesis contains several key ideas to support on-chip communication in the realm of 2D and 3D NoCs. The contributions of this dissertation with a brief summary are as follows:

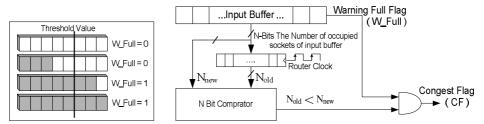

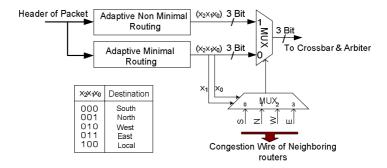

- An adaptive unicast routing algorithm in the realm of 2D-mesh NoCs is presented [36]. The routing algorithm, based on Dynamic XY (DyXY), is called Enhanced Dynamic XY (EDXY). It is an adaptive congestion-aware routing algorithm implemented by adding two congestion wires (one in each direction) between each two cores which indicate the existence of congestion in a row and a column. These signals enable the routing algorithm to avoid these paths when there are other paths between the source and destination pair.

- For both unicast and multicast traffic, two adaptive routing protocols are presented. The proposed routing protocols, named Low Distance (LD) [37][38] and Hamiltonian Adaptive Multicast Unicast Method (HAMUM) [39][40], maximize the degree of adaptiveness of the routing functions while guaranteeing deadlock freedom. The presented routing protocols invoke non-congested paths in routing the messages to prevent creating highly congested areas. This is achieved by considering the congestion condition of the input ports. Furthermore, both unicast and multicast aspects of the presented methods have been widely investigated separately.

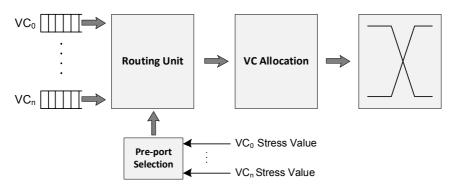

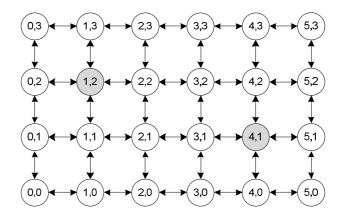

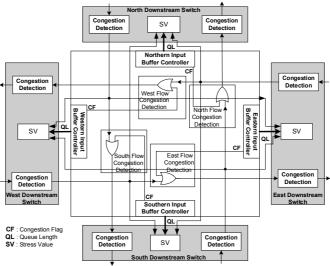

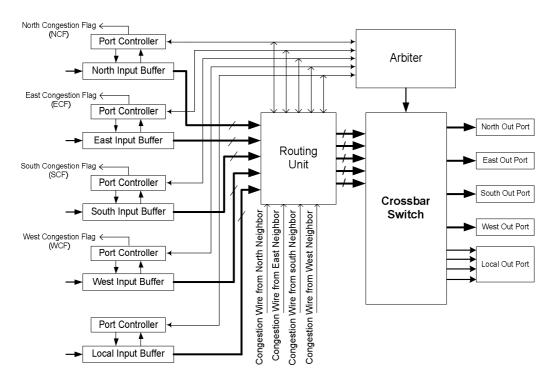

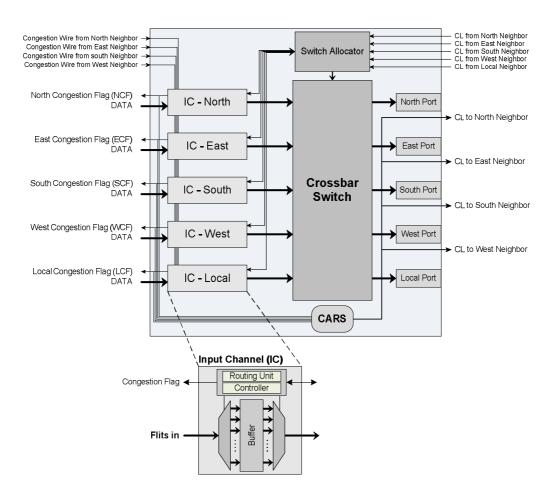

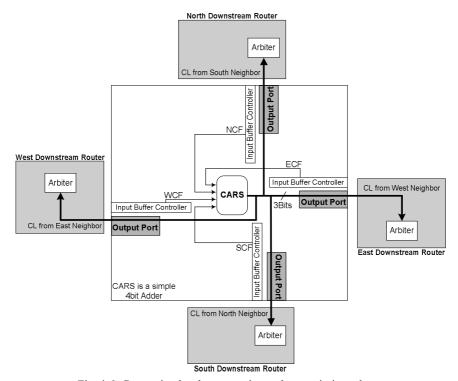

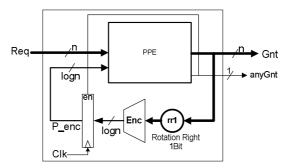

- To reduce the power consumption and improve the performance of on-chip networks, a novel on-chip router architecture is proposed. The router architecture, named Adaptive Input-Output Selection (AIOS), is for avoiding congested areas in 2D-mesh NoCs via employing efficient input and output selection [41][42][43]. The output selection utilizes an adaptive routing algorithm based on the congestion condition of neighboring routers while the input selection allows packets to be serviced from each input port according to its congestion level.

- To achieve higher memory bandwidth and increasing memory parallelism in network-based multiprocessor architectures, multiple SDRAMs can be accessed simultaneously.

In such architectures, not only resource utilization and latency are the critical issues but also a reordering mechanism is required to deliver the response transactions of

concurrent memory accesses in-order. To cope with these issues in this thesis, an adaptive on-chip network interface architecture is presented [44][45][46][47]. The proposed network interface exploits an efficient reordering mechanism to handle the in-order delivery and utilizes the AXI transaction based protocol to bring compatibility with existing IP cores. On top of that, a smart memory controller is integrated in this network interface to improve the memory utilization and reduce both memory and network latencies.

• To diminish the area overhead of TSVs and power dissipation on each layer with minimal performance penalty, two stacked structures for 3D architectures are proposed [48][49]. The presented schemes benefit of clustering the mesh topology in order to mitigate TSV footprint on each stacked layer. On top of that, to improve the performance of vertical channels, a new bus architecture is introduced [50]-[55]. The proposed bus architecture overcomes the drawbacks of previously presented buses, designed for vertical channels, and improves the performance by reducing the delay and complexity of traditional bus arbitration.

#### 1.5 Thesis Organization

This thesis is organized as follows. Chapter 2 gives a general overview of on-chip networks while Chapter 3 introduces three adaptive routing protocols, whereas the first one is related to the unicast traffic and the other two routing protocols are associated with unicast and multicast traffic. Two low latency and power efficient router architectures are presented in Chapter 4, while the adaptive network interface architecture for on-chip networks is described in Chapter 5. Concerning 3D architectures, two cluster-based topologies along with a novel pipeline bus architecture are explained in Chapter 6. The idea of the balance partitioning as well as multiple partitioning methods, supported by an adaptive routing model, is also presented in this chapter. Finally, the thesis is concluded in Chapter 7.

# Chapter 2

# **On-Chip Networks**

On-chip networks are emerged as a highly scalable, reliable, and modular interconnect fabric for MPSoCs [1][2][3][4][5]. As the network fabric takes up a substantial portion of system power budget [10], and power is one of the most important constraint in billion-transistor chips, in addition to network delay and area, the interconnect power consumption should be taken into consideration. Therefore, on-chip interconnection networks should be accommodated into the limited silicon area using efficient topology, routing algorithm, and router implementation.

In this chapter, concepts of on-chip networks including network topologies, switching techniques, flow control mechanisms, virtual channels, output selection, routing algorithms, and a general network-on-chip architecture are presented.

#### 2.1 Network Topology

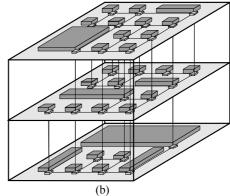

The network topology is the study of the arrangement and connectivity of the routers. In other words, it defines the various channels and the connection pattern that are available for the data transfer across the network. Performance, cost, and scalability are the important factors in the selection of the appropriate topology. Shared-Bus, Crossbar, Butterfly Fat-Tree, Ring, Torus, and 2D-Mesh are the most popular topologies for on-chip interconnects which have been commercially used [2][60].

Direct networks have at least one PE attached to each router of the network so that routers may regularly spread between PEs. This helps to simplify the physical implementation. The shared-bus, ring, and 2D mesh/torus topologies (Fig. 2-1) are examples of direct networks, and provide tremendous improvement in performance, but at a cost of hardware overhead, typically increasing as the square of the number of PEs. On the other hand, indirect networks have a subset of routers not connected to any PE. All tree-based topologies where PEs are connected only to the leaf routers (e.g. the butterfly topology) as well as crossbar switch (Fig. 2-1) are indirect networks.

The shared-bus topology is the simplest using a shared link common to all PEs where they compete for exclusive access to the bus. For communication intensive applications it is necessary to overcome the bandwidth limitations of the shared-bus topology and move to scalable networks. However, this topology scales very poorly as the number of PEs increases. A small modification to the shared-bus topology to allow more concurrent transactions is to create the ring topology where every PE has exactly two neighbors. In this topology, messages hop along intermediate PEs until they arrive at the final destination. This causes the ring to saturate at a low injection rate for most traffic patterns. The crossbar topology is a fully connected one which allows every PE to directly communicate with any other PE. Hence, each topology has its own advantages and disadvantages.

The fat-tree topologies suffer from the fact that the number of routers exceeds the number of PEs, when the amount of PEs increases. This incurs an important network overhead. For the on-chip interconnects the network overhead is more critical than for the off-chip networks, and the design scalability is more essential. Because of the simple connection and easy routing provided by adjacency, mesh and torus networks are widely used in multiprocessor architectures. Both torus and mesh topologies are fully scalable. Although torus provides a better performance, the regularity, better utilization of links, and lower network overhead are some of the preferences for mesh. That is, the mesh topology is more economic scheme since the routers on the borders are smaller.

#### 2.2 Switching Mechanism

The switching mechanism determines how messages traverse a route in a network. The goal is to effectively share the network resources among messages traversing the network. Basically, circuit switching and packet switching form the two extremes of switching mechanisms.

In circuit switching a connection from a source to a destination is established prior to the transmission of data and exclusively reserved until the message is completely transferred, i.e. as in telephone networks that set up a circuit through possibly many routers for each call. This mechanism has low delay and guaranteed bandwidths, but suffers from channel utilization, low throughput, and long initialization time to setup a connection.

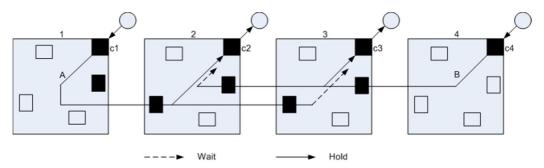

Packet switching is an alternative mechanism where data is not transmitted on a predefined circuit. A message can be divided into packets which share channels with other packets. Each packet consists of a header which contains routing and control information, data payload, and possibly a tail. The data payload follows the channel reserved by header while the tail releases the channel reservation. Packets are individually and independently routed through the network, and at the destination the packets are assembled into the original message. If a message is divided into several packets, the order of packets at arrival PE must be the same as departure. Therefore, in-order delivery is an essential part that should be supported by on-chip networks. The packet switching mechanism improves channel utilization and network throughput.

$Fig.\ 2\text{-}1.\ Network\ topologies\ of\ Shared-bus,\ Ring,\ Crossbar,\ Mesh,\ Torus,\ and\ Butterfly.$

In the packet switching domain, buffered flow control defines the mechanism that deals with the allocation of channels and buffers for the packets traversing between source and destination. The flow control mechanism is necessary when two or more packets compete to use the same channel, at the same time. Commonly three different buffered flow control strategies are used: store-and-forward, virtual cut through, and wormhole. When these mechanisms are implemented in on-chip networks, they have different performance metrics along with different requirements on hardware resources.

#### 2.2.1 Store-and-Forward

The store-and-forward mechanism is the simplest flow control mechanism. In this approach, each router along the path stores the entire packet in the buffer and then, the packet is forwarded to a selected neighboring router if the chosen neighboring router has enough empty buffering space available to hold the whole packet. This mechanism requires a large amount of buffering space (at least the size of the largest packet) in each router of the network, which can increase the implementation cost dramatically. On top of that, network latency increases significantly because a packet cannot be forwarded to the next router until the whole packet is received and stored in the current router. Consequently, the store-and-forward approach is impractical in large-scale Networks-on-Chip.

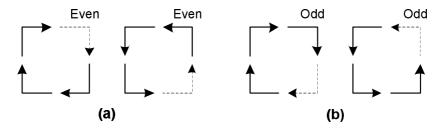

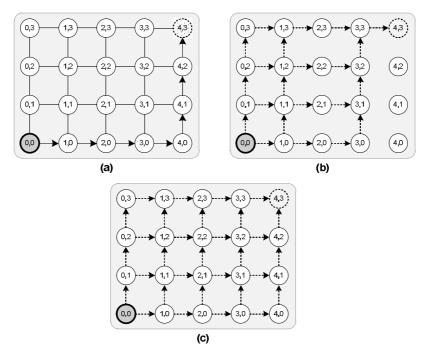

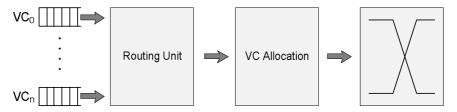

#### 2.2.2 Virtual Cut-Through