#### TURUN YLIOPISTON JULKAISUJA ANNALES UNIVERSITATIS TURKUENSIS

SARJA - SER. A I OSA - TOM. 465

ASTRONOMICA - CHEMICA - PHYSICA - MATHEMATICA

# ADAPTIVE ROUTING APPROACHES FOR NETWORKED MANY-CORE SYSTEMS

by

Masoumeh Ebrahimi

TURUN YLIOPISTO UNIVERSITY OF TURKU Turku 2013 From the Laboratory of Embedded Computer and Electronic Systems, ECES

Department of Information Technology

University of Turku

Turku, Finland

&

Graduate School in Electronics, Telecommunications and Automation, GETA

Aalto University

Helsinki, Finland

# **Supervisors**

Professor Hannu Tenhunen Associate Professor Juha Plosila Associate Professor Pasi Liljeberg Department of Information Technology University of Turku Turku, Finland

### **Reviewers**

Professor Nader Bagherzadeh Department of Electrical Engineering and Computer Science University of California Irvine, US

Professor Thomas Hollstein Department of Computer Engineering Tallin University of Technology Tallin, Estonia

# **Opponent**

Professor Paolo Ernesto Prinetto Department of Control and Computer Engineering Polytechnic University of Turin Turin, Italy

ISBN 978-951-29-5453-7 ISSN 0082-7002 Painosalama Oy-Turku, Finland 2012

# **Abstract**

Through advances in technology, System-on-Chip design is moving towards integrating tens to hundreds of intellectual property blocks into a single chip. In such a many-core system, on-chip communication becomes a performance bottleneck for high performance designs. Network-on-Chip (NoC) has emerged as a viable solution for the communication challenges in highly complex chips. The NoC architecture paradigm, based on a modular packet-switched mechanism, can address many of the on-chip communication challenges such as wiring complexity, communication latency, and bandwidth. Furthermore, the combined benefits of 3D IC and NoC schemes provide the possibility of designing a high performance system in a limited chip area. The major advantages of 3D NoCs are the considerable reductions in average latency and power consumption.

There are several factors degrading the performance of NoCs. In this thesis, we investigate three main performance-limiting factors: network congestion, faults, and the lack of efficient multicast support. We address these issues by the means of routing algorithms.

Congestion of data packets may lead to increased network latency and power consumption. Thus, we propose three different approaches for alleviating such congestion in the network. The first approach is based on measuring the congestion information in different regions of the network, distributing the information over the network, and utilizing this information when making a routing decision. The second approach employs a learning method to dynamically find the less congested routes according to the underlying traffic. The third approach is based on a fuzzy-logic technique to perform better routing decisions when traffic information of different routes is available.

Faults affect performance significantly, as then packets should take longer paths in order to be routed around the faults, which in turn increases congestion around the faulty regions. We propose four methods to tolerate faults at the link and switch level by using only the shortest paths as long as such path exists. The unique characteristic among these methods is the toleration of faults while also maintaining the performance of NoCs. To the best of our knowledge, these algorithms are the first approaches to bypassing faults prior to reaching them while avoiding unnecessary misrouting of packets.

Current implementations of multicast communication result in a significant performance loss for unicast traffic. This is due to the fact that the routing rules of multicast packets limit the adaptivity of unicast packets. We present an approach in which both unicast and multicast packets can be efficiently routed within the network. While suggesting a more efficient multicast support, the proposed approach does not affect the performance of unicast routing at all. In addition, in order to reduce the overall path length of multicast packets, we present several partitioning methods along with their analytical models for latency measurement. This approach is discussed in the context of 3D mesh networks.

# Acknowledgements

It has been a great privilege to make my doctoral studies at the Department of Information Technology, university of Turku, Finland since March 2009. I would like to express my deepest appreciation to all those who have made some contributions in this way. The valuable experience that I have gained in this period is tightly connected to all people around me as my wonderful supervisors, helpful staff, friendly colleagues, and my lovely husband-colleague.

Special gratitude I give to my supervisors, Professor Hannu Tenhunen, Associate professor Juha Plosila, and Associate professor Pasi Liljeberg for their excellent guidance, continuous support, patience against any issues, and providing me with an excellent atmosphere for doing research. There are much more appreciations but I fall short of words. I would really mean by saying that I could have ever imagined having better supervisors than them! Beside my supervisors, I would also like to acknowledge the crucial role of Doctor Masoud Daneshtalab for his valuable comments, advice, and insight throughout my work. This thesis would not have been possible without his stimulating suggestions and encouragement throughout these years.

I wish to thank the pre-examiners, Professor Nader Bagherzadeh and Professor Thomas Hollstein for their constructive comments and suggestions on the thesis. Special thanks go to Professor Paolo Prinetto for accepting to act as my opponent.

The research was mainly funded by the graduate school in Electronics, Telecommunications, and Automation (GETA). I would like to thank GETA and its staff for the financial, academic, and technical support. In addition, I greatly appreciate the financial support by Nokia and Elisa Foundation. Furthermore, I would like to acknowledge the Business and Innovation Development (BID) and European Institute of Innovation and Technology (EIT ICT Labs) for their support to follow the MBA program along with the doctoral studies and being involved in ICT innovation and entrepreneurship activities.

I have had an opportunely to do a research visit at the University of Toronto, Canada. I wish to thank Professor Natalie Jerger for the invitation and valuable discussions.

I wish to thank my parents and family for their continuous love and inspiration. I could say the most difficult part of this thesis was to be far from them! They are the most valuable things to me. I wish I could express how much I love and appreciate them.

I would like to thank Masoud again, but this time as my beloved one. He has supported me throughout the entire process not only by his academic guidance and encouragement but also spiritually by his pure love! Masoud is the one who made my dreams reality and constantly giving me a wonderful feeling of unlimited love!

Last but not the least, I want to thank my lovely friends Anne-Marie Tuikka and Fahime Farahnakian for having delightful coffee breaks, helping me to refresh my mind!

# **Contents**

| 1 | Intro | luction                                                  | 1  |

|---|-------|----------------------------------------------------------|----|

|   | 1.1 T | hesis Contributions                                      | 2  |

|   | 1.1.1 | Congestion-aware Techniques                              | 3  |

|   | 1.1.2 | Fault-Tolerant Techniques                                | 4  |

|   | 1.1.3 | Collective Communication                                 | 5  |

|   | 1.2 T | hesis Organization                                       | 6  |

| 2 | Netwo | orks-on-Chip                                             | 11 |

|   | 2.1 N | Networks-on-Chip Characteristics                         | 11 |

|   | 2.1.1 |                                                          |    |

|   | 2.1.2 | Network Topology                                         |    |

|   | 2.1.3 | Switch Architecture                                      |    |

|   | 2.1.4 | Virtual Channel                                          | 13 |

|   | 2.1.5 | Switching Techniques                                     | 14 |

|   | 2.1.6 | Flow Control Mechanisms                                  | 14 |

|   | 2.2 R | Couting Algorithms                                       | 15 |

|   | 2.2.1 | Deterministic and Adaptive Routing                       |    |

|   | 2.2.2 | Minimal and Non-minimal Routing                          |    |

|   | 2.2.3 | Congestion-aware and Congestion-oblivious Routing        |    |

|   | 2.2.4 | Unicast and Multicast Routing                            | 16 |

|   | 2.2.5 | Fault-Tolerant Routing                                   | 17 |

|   | 2.2.6 | Starvation, Deadlock, and Livelock                       | 17 |

|   | 2.2.7 | Turn Models                                              | 18 |

| 3 | Conge | estion-Aware Routing Algorithms for a 2D Mesh Network    | 19 |

|   | 3.1 T | raditional Approaches                                    | 19 |

|   | 3.1.1 | Dynamic XY (DyXY)                                        | 20 |

|   | 3.1.2 | Enhanced Dynamic XY (EDXY)                               | 20 |

|   | 3.1.3 | Neighbor-on-Path (NoP)                                   | 21 |

|   | 3.1.4 | Regional Congestion Awareness (RCA)                      | 22 |

|   | 3.1.5 | Destination-Based Adaptive Routing (DBAR)                | 23 |

|   | 3.1.6 | Q-Learning Approach with Reduced Table Sizes (C-Routing) |    |

|   | 3.1.7 | Summary of Traditional Methods                           | 25 |

|   | 3.2 T | The Proposed Cluster-based Approaches                    | 25 |

|   |       | Agent-based Routing Algorithm (AgRA)                     |    |

|   |       |                                                          |    |

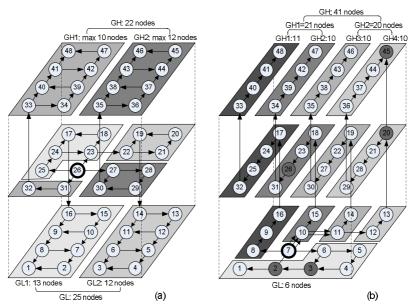

|   | 3.2.2 Trapezoid-based Routing Algorithm (TRA)                 | 29        |

|---|---------------------------------------------------------------|-----------|

|   | 3.2.3 Results and Discussion                                  |           |

|   | 3.3 The Proposed Non-Minimal and Learning-based Approache     | es43      |

|   | 3.3.1 Highly Adaptive Non-Minimal Routing Algorithm (HAR      | AA)44     |

|   | 3.3.2 Q-Learning-based Approach using HARA (HARAQ)            | 50        |

|   | 3.3.3 Results and Discussion                                  | 54        |

|   | 3.4 The Proposed Fuzzy-based Approach                         | 57        |

|   | 3.4.1 Non-Fuzzy Routing Algorithm (NFRA)                      |           |

|   | 3.4.2 Fuzzy-based Routing Algorithm (FRA)                     |           |

|   | 3.4.3 Results and Discussion                                  | 69        |

|   | 3.5 Summary of the Proposed Methods                           | 72        |

| 4 | 4 Fault-Tolerant Routing Algorithms for a 2D Mesh Network.    | 75        |

|   | 4.1 Traditional Approaches                                    | 76        |

|   | 4.1.1 A Ring-based Fault-Tolerant Routing (Extended X-Y)      | 76        |

|   | 4.1.2 Reconfigurable Routing for Tolerating Faulty Switches ( |           |

|   | 4.1.3 Reconfigurable Routing for Tolerating Faulty Links (RA  |           |

|   | 4.1.4 Bidirectional Fault-Tolerant NoC (BFT-NoC)              |           |

|   | 4.1.5 Summary of Traditional Methods                          | 78        |

|   | 4.2 The Proposed Approaches for Tolerating Faulty Links       | 79        |

|   | 4.2.1 Any Single Faulty Link (MD)                             | 79        |

|   | 4.2.2 Multiple Faulty Links (MAFA)                            |           |

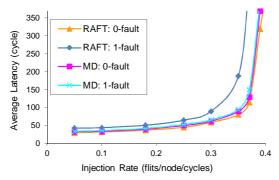

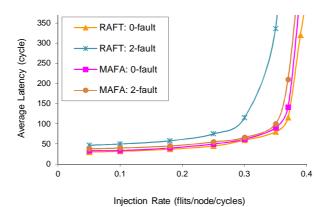

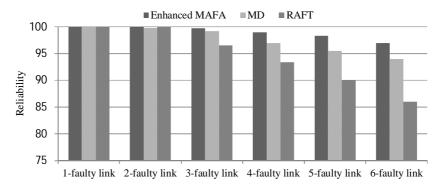

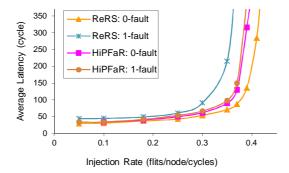

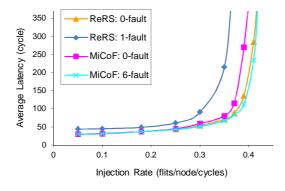

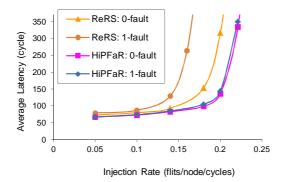

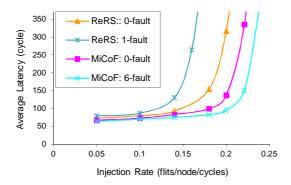

|   | 4.2.3 Results and Discussion                                  | 96        |

|   | 4.3 The Proposed Approaches for Tolerating Faulty Switches    | 99        |

|   | 4.3.1 Any Single Faulty Switch (HiPFaR)                       | 99        |

|   | 4.3.2 Multiple Faulty Switches (MiCoF)                        |           |

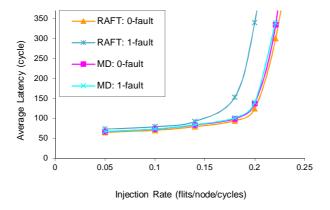

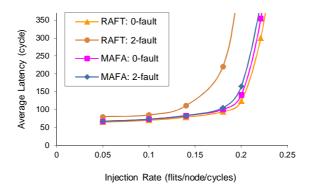

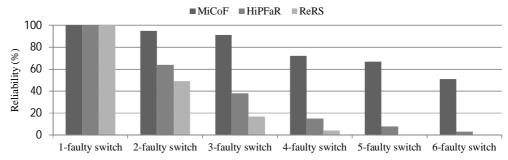

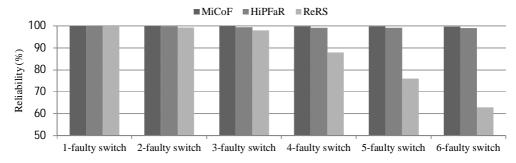

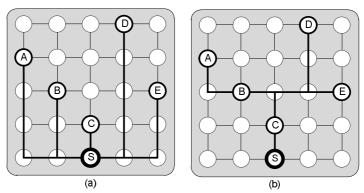

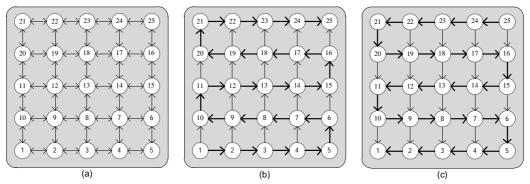

|   | 4.3.3 Results and Discussion                                  | 112       |

|   | 4.4 Summary of the Proposed Methods                           | 116       |

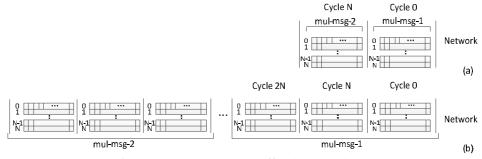

| 5 | 5 Unicast and Multicast Routing Algorithms for a 3D Mesh Ne   | etwork119 |

|   | 5.1 Traditional Approaches                                    | 120       |

|   | 5.1.1 Virtual Circuit Tree Multicasting (VCTM)                | 120       |

|   | 5.1.2 Dual-Path Multicast Routing (DP)                        |           |

|   | 5.1.3 Multi-Path Multicast Routing (MP)                       | 123       |

|   | 5.1.4 Hamiltonian Adaptive Multicast and Unicast Model (HA    |           |

|   | 5.1.5 Summary of Traditional Methods                          | 124       |

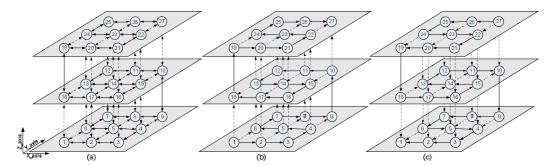

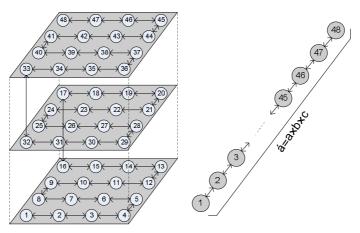

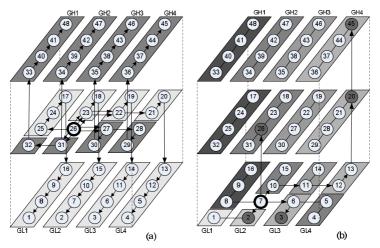

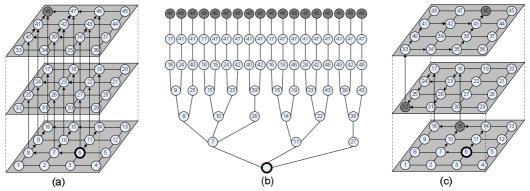

|   | 5.2 The Proposed Partitioning Methods for a 3D Mesh Network   | c 125     |

|   | 5.2.1 Hamiltonian Path in a 3D Mesh Network                   | 125       |

|   | 5.2.2 Two-Block Partitioning Method (TBP)                     |           |

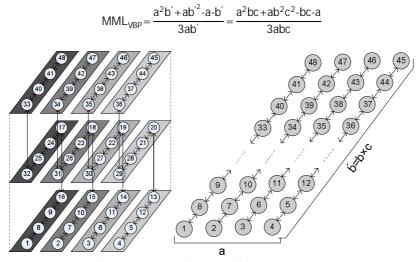

|   | 5.2.3 Vertical Block Partitioning (VBP)                       | 130       |

| 6 Conclusion                                | 151 |

|---------------------------------------------|-----|

| 5.5 Summary of the Proposed Methods         | 150 |

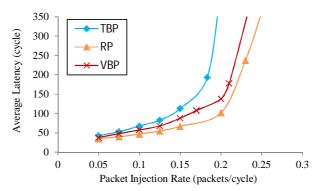

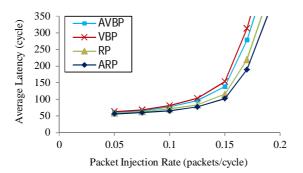

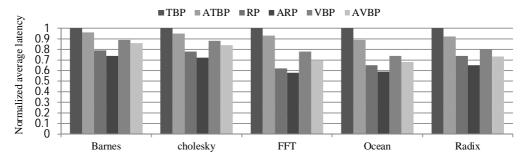

| 5.4.2 Simulation Results                    | 143 |

| 5.4.1 Analytical Results                    | 140 |

| 5.4 Results and Discussion                  | 140 |

| 5.3.2 Deadlock Avoidance                    |     |

| 5.3.1 Minimal Adaptive Routing (MAR)        |     |

| 5.3 The Proposed Adaptive Routing Algorithm | 136 |

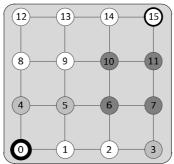

| 5.2.4 Recursive Partitioning (RP)           | 133 |

# **List of Figures**

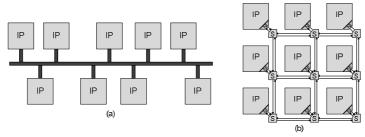

| 1.1: (a) Bus (b) Network-on-Chip                                                           | 1   |

|--------------------------------------------------------------------------------------------|-----|

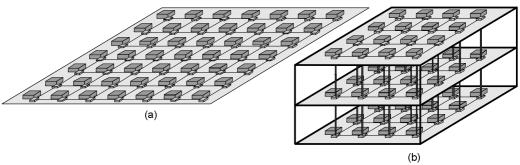

| 2.1: (a) 2D NoC (b) 3D NoC                                                                 |     |

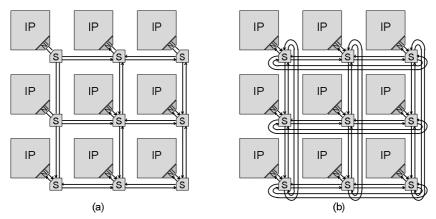

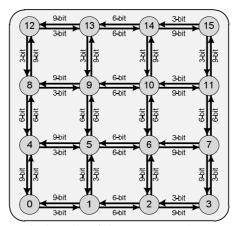

| 2.2: (a) Mesh topology (b) Torus topology                                                  | 12  |

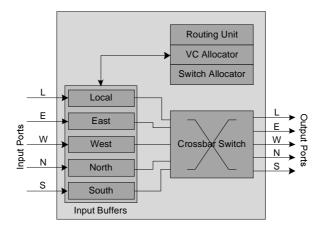

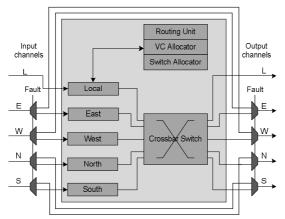

| 2.3: A switch architecture                                                                 | 13  |

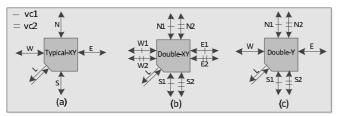

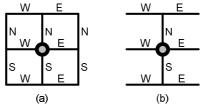

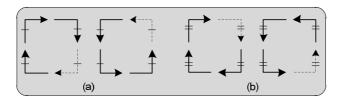

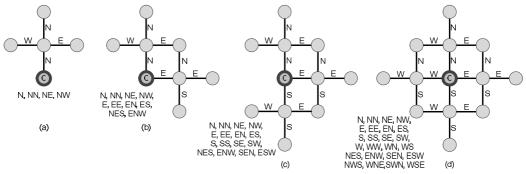

| 2.4: A switch in (a) XY (b) double-XY (c) double-Y network                                 | 14  |

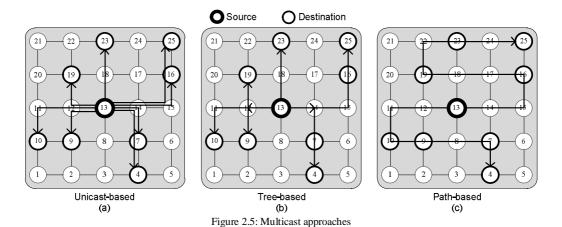

| 2.5: Multicast approaches                                                                  | 17  |

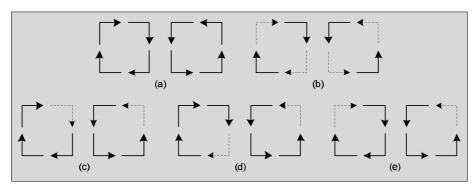

| 2.6: (a) Clockwise and counter-clockwise turns (b) XY routing (c) Negative-First (d) We    | st- |

| First (e) North-Last (Solid lines indicate the allowable turns and dash lines indicate the | the |

| prohibited turns)                                                                          | 18  |

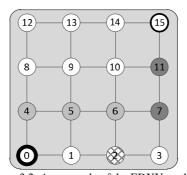

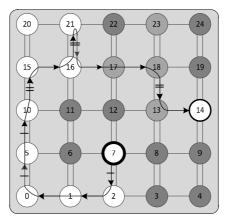

| 3.1: An example of the DyXY method                                                         | 20  |

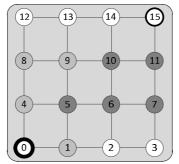

| 3.2: An example of the EDXY method                                                         | 21  |

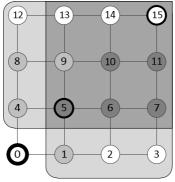

| 3.3: An example of the NoP method                                                          |     |

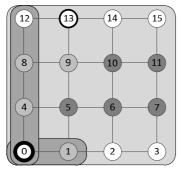

| 3.4: An example of the RCA method                                                          | 23  |

| 3.5: An example of the DBAR method                                                         | 24  |

| 3.6: An example of the learning-based approach                                             | 25  |

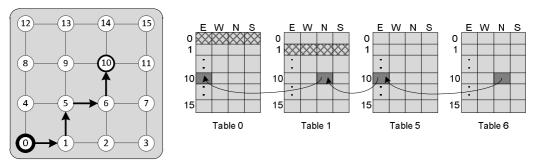

| 3.7: Agent-based Networks-on-Chip                                                          |     |

| 3.8: The congestion-aware selection algorithm in the agent-based approach                  | 28  |

| 3.9: An example of the agent-based selection method                                        |     |

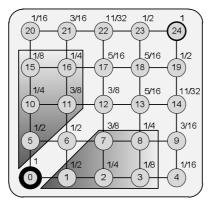

| 3.10: Passing-probability of packets through intermediate switches                         | 31  |

| 3.11: The output selection function of TRA                                                 |     |

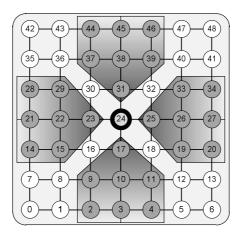

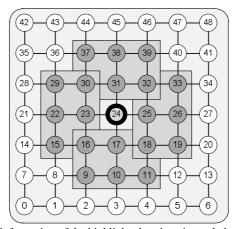

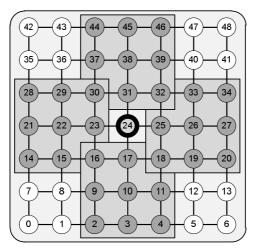

| 3.12: The congestion information of the highlighted regions is needed at the switch 24 to  |     |

| perform the output selection function of TRA                                               | 33  |

| 3.13: Input selection function of TRA                                                      |     |

| 3.14: The congestion information of the highlighted regions is needed at the switch 24 to  |     |

| perform the input selection function of TRA                                                |     |

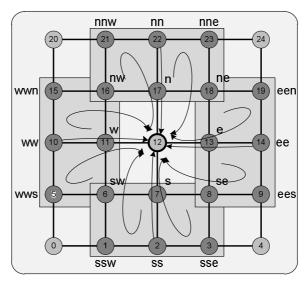

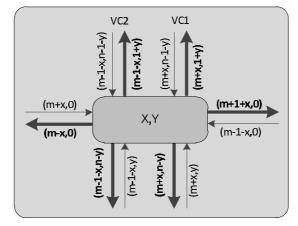

| 3.15: Assigning a name to each switch                                                      | 35  |

| 3.16: Assigning congestion values to packets                                               |     |

| 3.17: The pseudo code of the priority-based input selection function of TRA                |     |

| 3.18: A general example of combining the input and output selection functions of TRA       |     |

| 3.19: The required information at the switch 24 to perform the input and output selection  |     |

| functions                                                                                  | 38  |

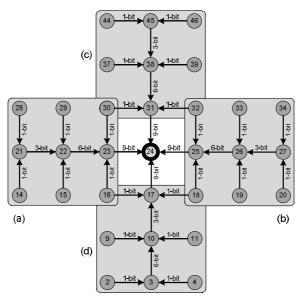

| 3.20: Information from (a) west- (b) east- (c) north-, and (d) south-ward regions to the   |     |

| switch 24                                                                                  |     |

| 3.21: The required number of bits to propagate the congestion information                  |     |

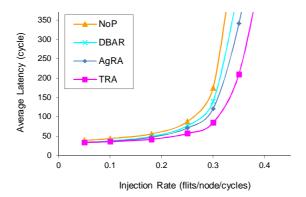

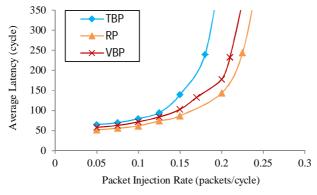

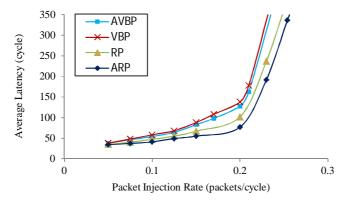

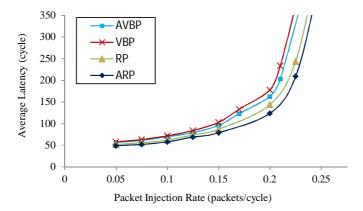

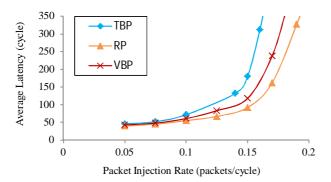

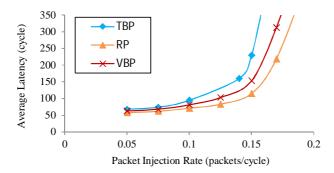

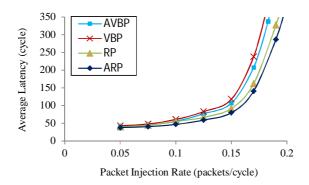

| 3.22: Performance analysis in an 8×8 mesh network under uniform traffic profile            | 41  |

| 3.23: Performance analysis in an 8×8 mesh network under hotspot traffic profile with       |     |

| H=10%                                                                                      |     |

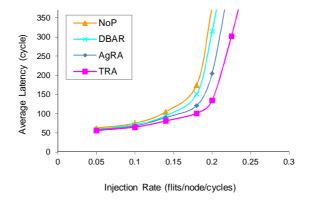

| 3.24: Performance analysis under different application benchmarks normalized to NoP        | 43  |

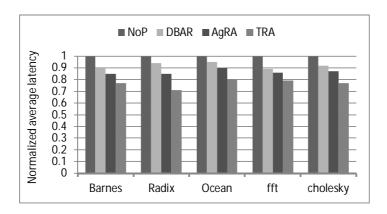

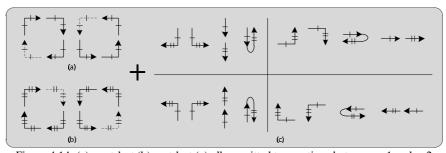

| 3.25: (a) A switch in a double-Y network (b) 0-degree-ch (c) 0-degree-vc (d) 90-degree    | (e)  |

|-------------------------------------------------------------------------------------------|------|

|                                                                                           | 45   |

| 3.26: (a) 90-degree turns in vc1 (b) 90-degree turns in vc2 (c) 0-degree-ch (d) 0-degree- |      |

|                                                                                           |      |

| 3.27: Channel numbering in the Mad-y method                                               |      |

| 3.28: Allowable 180-degree turns in the HARA method                                       |      |

| 3.29: The numbering mechanism of HARA                                                     | 47   |

| 3.30: All eligible turns in HARA                                                          | 47   |

| 3.31: Determining all eligible output channels by HARA                                    |      |

| 3.32: An example of HARA                                                                  |      |

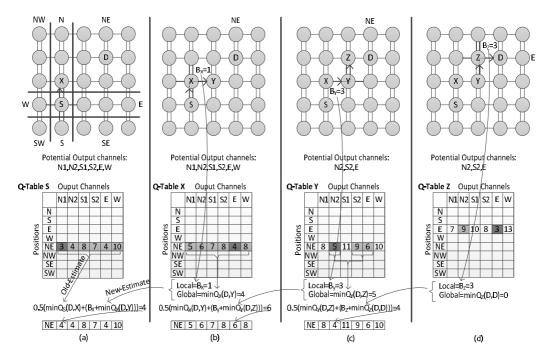

| 3.33: The process of updating the Q-Tables                                                | 52   |

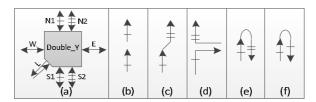

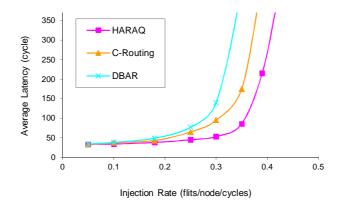

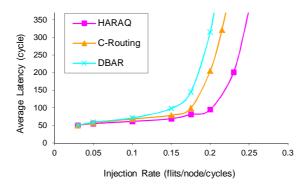

| 3.34: Performance analysis in an 8×8 mesh network under the uniform traffic profile       | 55   |

| 3.35: Performance analysis in an 8×8 mesh network under hotspot traffic profile with      |      |

| H=10%                                                                                     |      |

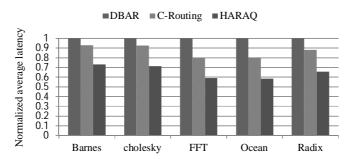

| 3.36: Performance analysis under different application benchmarks normalized to DBAI      |      |

| 3.37: Non-optimal decision by the DyXY routing algorithm                                  | 58   |

| 3.38: The pseudo code of NFRA                                                             |      |

| 3.39: Two examples of non-optimal routing decisions in NFRA                               | 60   |

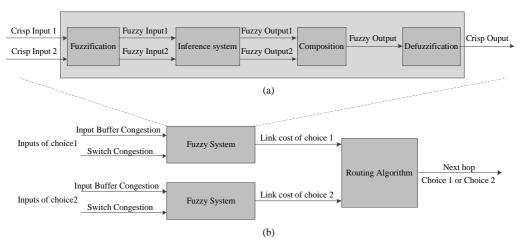

| 3.40: (a) General fuzzy system (b) Fuzzy routing algorithm                                | 61   |

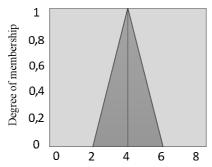

| 3.41: An example of triangular membership function                                        | 62   |

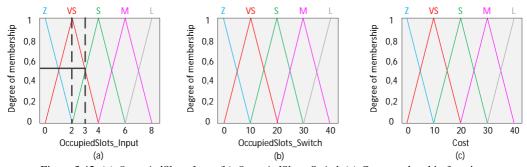

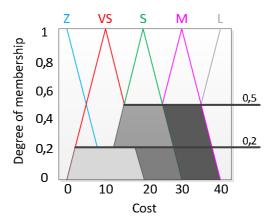

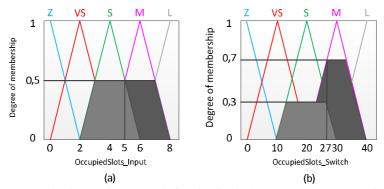

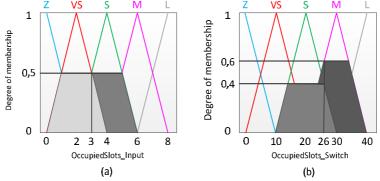

| 3.42: (a) OccupiedSlots_Input (b) OccupiedSlots_Switch (c) Cost membership function       | s 63 |

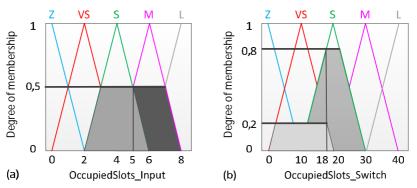

| 3.43: (a) OccupiedSlots_Input (b) OccupiedSlots_Switch as a part of two membership        |      |

| functions                                                                                 |      |

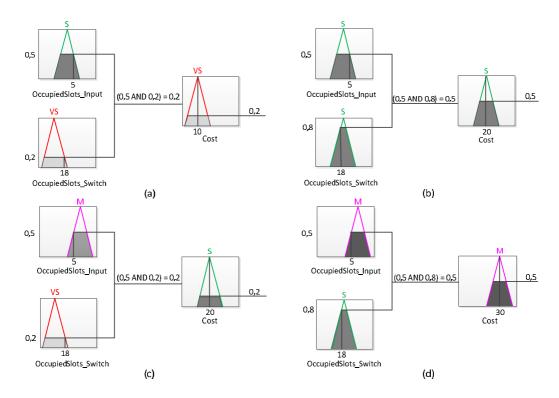

| 3.44: Cost for (a) rule1 (b) rule2 (c) rule3 (d) rule4                                    | 66   |

| 3.45: Composition of the Cost membership function of all rules                            |      |

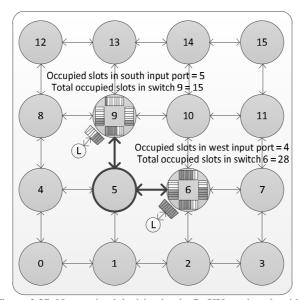

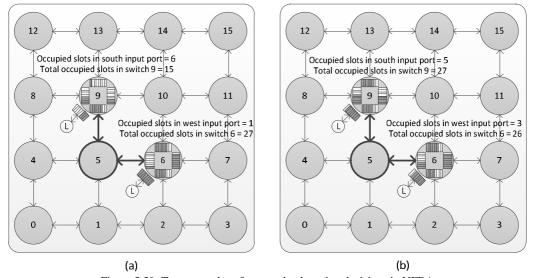

| 3.46: The degree of membership function for the input parameters at the switch 9          |      |

| 3.47: The degree of membership function for the input parameters at the switch 6          |      |

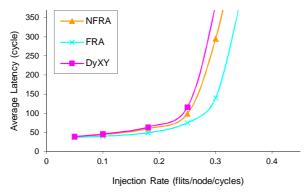

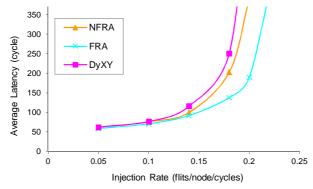

| 3.48: Performance analysis in an 8×8 mesh network under the uniform traffic profile       | 70   |

| 3.49: Performance analysis in an 8×8 mesh network under hotspot traffic profile with      |      |

| H=10%                                                                                     |      |

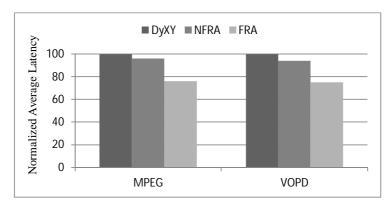

| 3.50: Simulation results under two multimedia traffic profiles: MPEG and VOPD             | 71   |

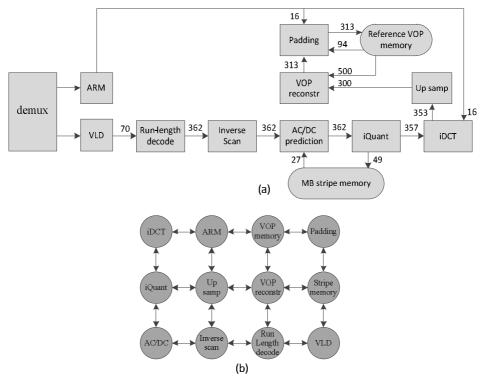

| 3.51: (a) VOPD block diagram, with communication BW annotated (in MB/s) (b) its           |      |

| mapping onto a mesh topology [19]                                                         |      |

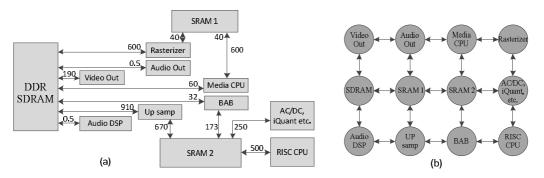

| 3.52: (a) MPEG4 decoder block diagram, with communication BW annotated (in MB/s)          |      |

| its mapping onto a mesh topology [19]                                                     | 72   |

| 4.1: (a) Two examples of the Extended X-Y routing algorithm (b) The required fault        |      |

|                                                                                           | 77   |

| 4.2: (a) Two examples of the ReRS routing algorithm (b) The required fault information    |      |

| 4.3: (a) Two examples of the RAFT routing algorithm (b) The required fault information    | n 78 |

| 4.4: (a) Statuses of twelve links are needed by RAFT (b) The statuses of eight links are  |      |

|                                                                                           | 79   |

| 4.5: Permitted and prohibited turns of MD similar to Mad-y                                |      |

| 4.6: The numbering mechanism of MD similar to Mad-y                                       | 80   |

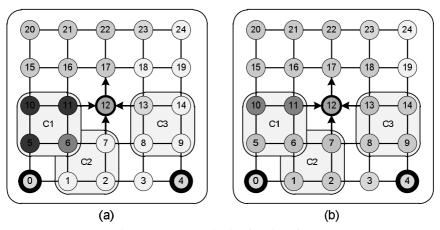

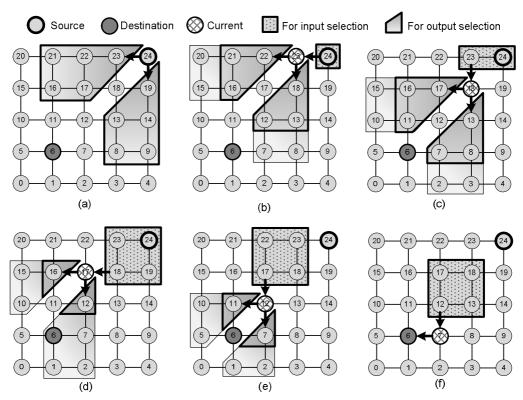

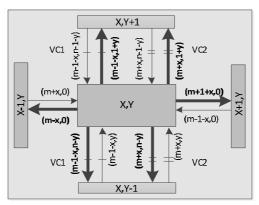

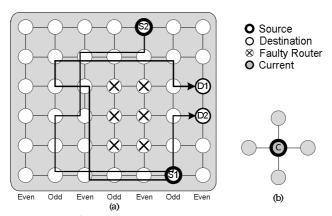

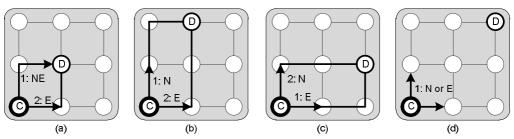

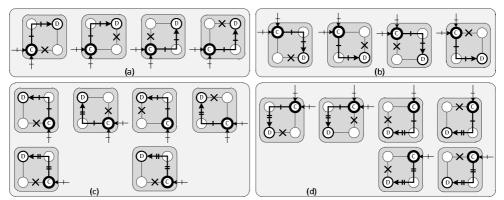

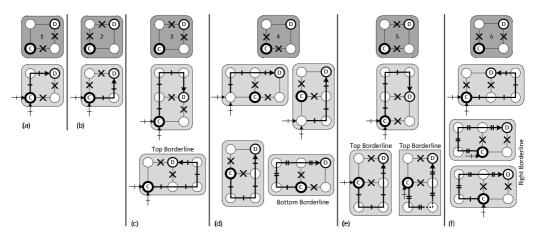

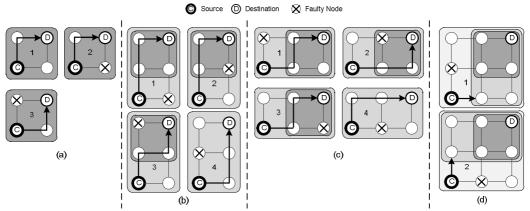

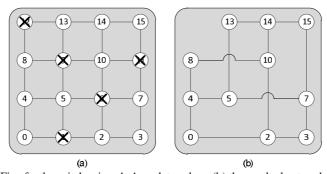

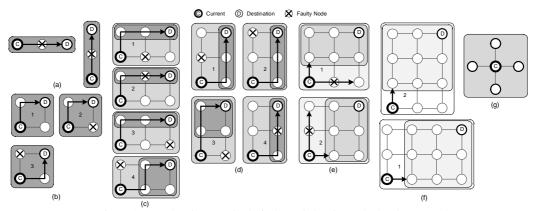

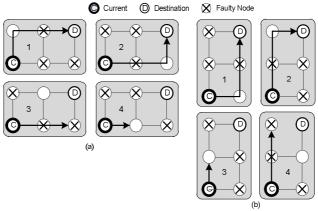

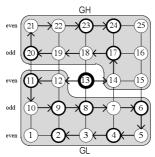

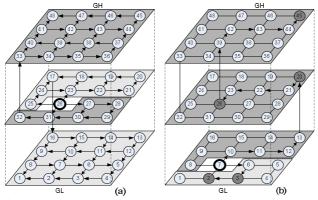

| 4.7: Bypassing faulty links when the destination is located in the northeast position                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| source switch (Note that numbers determine the priority of selecting among d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |

| routes)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |

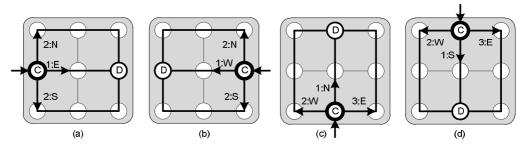

| 4.8: Bypassing faulty links when the destination is located in the (a) east (b) west (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

| (d) south positions of the source switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

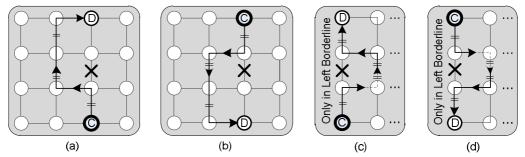

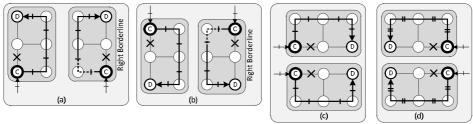

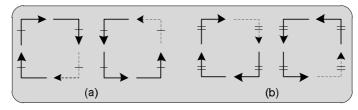

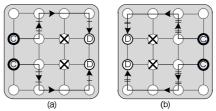

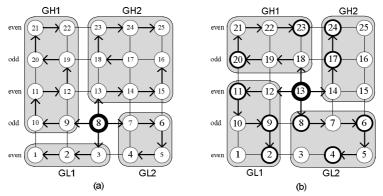

| 4.9: Northward and southward packets are strictly belonging to the second virtual of the |            |

| (a) and (b) show the cases where the fault does not occur in the left borderline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |

| (d) show how the fault can be tolerated when the fault occur in the left border                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

| 4.10: MD routing algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |

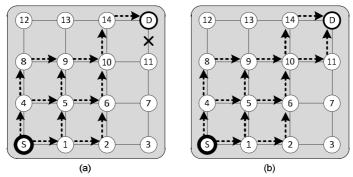

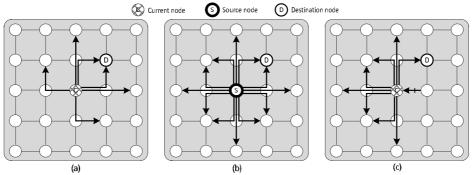

| 4.11: Alternative paths from the source switch S to the destination D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |

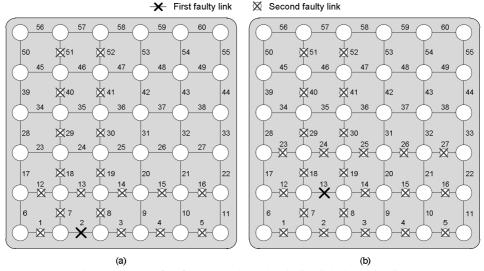

| 4.12: The first fault occurs in (a) borderline link (b) central link                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

| 4.13: Fault distribution mechanism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

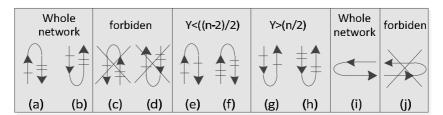

| 4.14: (a) west-last (b) east-last (c) all permitted transactions between vc1 and vc2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

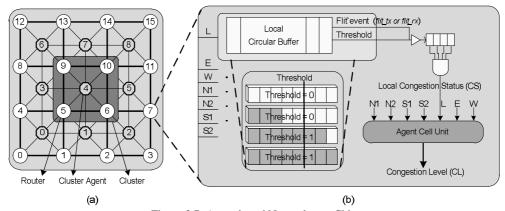

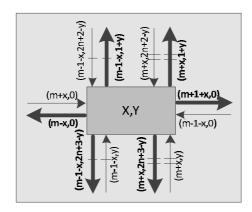

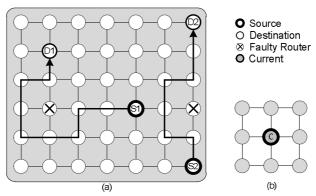

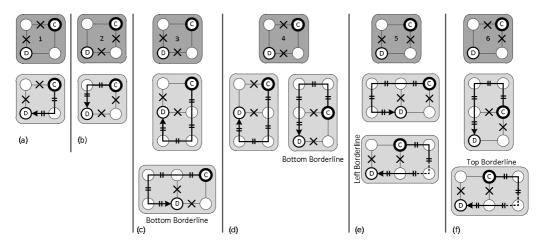

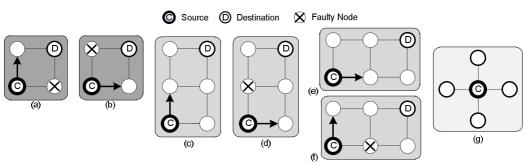

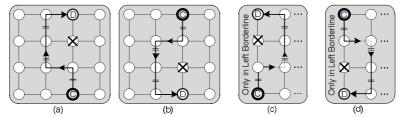

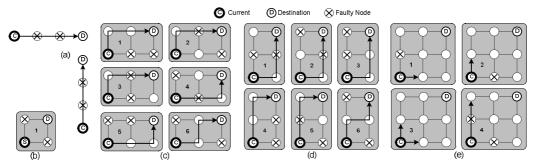

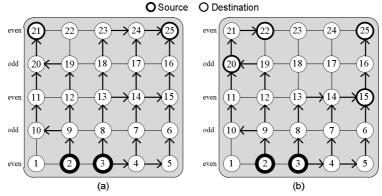

| 4.15: Tolerating one faulty link by MAFA when the destination is in the (a) norther                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |

| southeast (c) northwest (d) southwest of the current switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |

| 4.16: Tolerating one faulty link by MAFA when the destination is in the (a) north (c) east (d) west positions of the current switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |

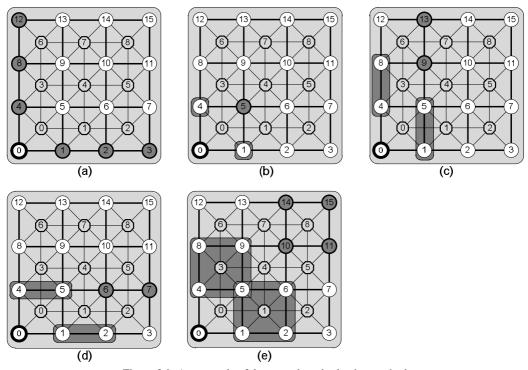

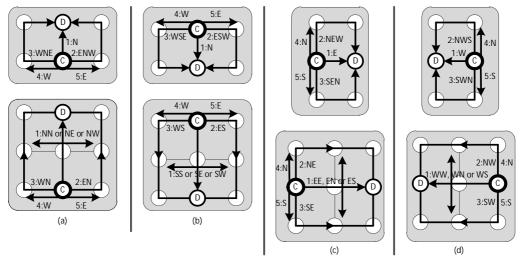

| 4.17: Priority of selecting among different routes when the destination is in the (a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |

| (b) southeast (c) northwest (d) southwest positions of the current switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |

| 4.18: Different positions of two faulty links for a northeast packet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

| 4.19: Different positions of two faulty links for a southwest packet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

| 4.20: Priority of different routes for (a) northward (b) southward (c) eastward (d) w                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |

| packets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |

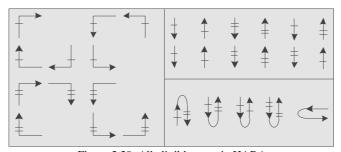

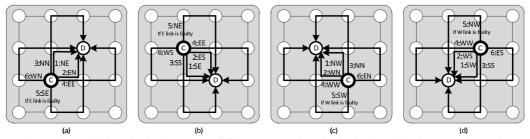

| 4.21: MAFA routing algorithm for northeast, northwest, southeast, and southwest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | nackets    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

| 4.22: MAFA routing algorithm for north-, south-, east-, and west-ward packets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |

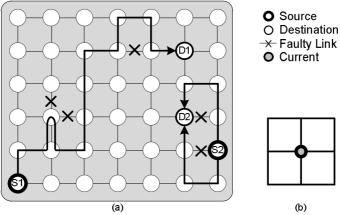

| 4.23: Examining all possible paths by Enhanced MAFA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |

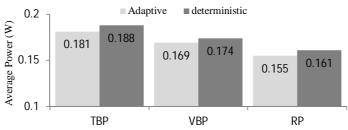

| 4.24: Non-minimal choices offered by Enhanced-MAFA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |