## Khalid Latif

# Design Space Exploration for MPSoC Architectures

TURKU CENTRE for COMPUTER SCIENCE

TUCS Dissertations No 166, December 2013

# Design Space Exploration for MPSoC Architectures

## Khalid Latif

To be presented with the permission of the Faculty of Mathematics and Natural Sciences of the University of Turku, for public criticism in Auditorium Beta on December 20, 2013, at 9:00 am.

University of Turku Department of Information Technology 20014 Turun yliopisto

2013

### **Supervisors**

Docent Tiberiu Seceleanu ABB Corporate Research, Västerås Västerås, Sweden

Professor Hannu Tenhunen

D.Sc. (Tech.) Ethiopia Nigussie

Department of Information Technology

University of Turku

Turku, Finland

#### Reviewers

Professor Olli Vainio Department of Computer Systems Tampere University of Technology Tampere, Finland

Associate Professor Marisa López-Vallejo Departamento de Ingeniería Electrónica E.T.S.I. Telecomunicación Universidad Politécnica de Madrid Madrid, Spain

## Opponent

Professor Koen Bertels Computer Engineering, EEMCS Delft University of Technology Delft, The Netherlands

ISBN 978-952-12-2976-3 ISSN 1239-1883

The originality of this thesis has been checked in accordance with the University of Turku quality assurance system using the Turnitin OriginalityCheck service.

## Abstract

Multiprocessor system-on-chip (MPSoC) designs utilize the available technology and communication architectures to meet the requirements of the upcoming applications. In MPSoC, the communication platform is both the key enabler, as well as the key differentiator for realizing efficient MPSoCs. It provides product differentiation to meet a diverse, multi-dimensional set of design constraints, including performance, power, energy, reconfigurability, scalability, cost, reliability and time-to-market. The communication resources of a single interconnection platform cannot be fully utilized by all kind of applications, such as the availability of higher communication bandwidth for computation but not data intensive applications is often unfeasible in the practical implementation.

This thesis aims to perform the architecture-level design space exploration towards efficient and scalable resource utilization for MPSoC communication architecture. In order to meet the performance requirements within the design constraints, careful selection of MPSoC communication platform, resource aware partitioning and mapping of the application play important role. To enhance the utilization of communication resources, variety of techniques such as resource sharing, multicast to avoid re-transmission of identical data, and adaptive routing can be used. For implementation, these techniques should be customized according the platform architecture. To address the resource utilization of MPSoC communication platforms, variety of architectures with different design parameters and performance levels, namely Segmented bus (SegBus), Network-on-Chip (NoC) and Three-Dimensional NoC (3D-NoC), are selected. Average packet latency and power consumption are the evaluation parameters for the proposed techniques.

In conventional computing architectures, fault on a component makes the connected fault-free components inoperative. Resource sharing approach can utilize the fault-free components to retain the system performance by reducing the impact of faults. Design space exploration also guides to narrow down the selection of MPSoC architecture, which can meet the performance requirements with design constraints.

Dedicated to my late parents Who believed in the richness of learning

## Acknowledgements

It gives me great pleasure to be able to express my gratitude to the people and institutions that have helped me to accomplish this research work. First and foremost, I would like to thank my supervisors Docent Tiberiu Seceleanu, D.Sc. (Tech.) Ethiopia Nigussie, and Prof. Hannu Tenhunen for their inspiration, guidance and support.

I owe a huge debt of thanks to Docent Tiberiu Seceleanu for his invaluable and continuous guidance. His comments and criticism had a significant impact on the research presented here. I am very grateful to D.Sc. (Tech.) Ethiopia Nigussie for her guidance and encouragement throughout the period of my research. I am also indebted to Prof. Hannu Tenhunen for inspiring me to pursue my research in on-chip interconnection platforms. I wish to thank Prof. Olli Vainio from the Tampere University of Technology, Finland and Associate Professor Marisa López-Vallejo from Universidad Politécnica de Madrid, Spain for reviewing the thesis.

Turku Centre for Computer Science (TUCS) is gratefully acknowledged for funding my doctoral studies. This research work was also financially supported by the Academy of Finland, the Nokia Foundation, the Finnish Foundation for Technology Promotion (Tekniikan edistämissäätiö (TES)), the HPY:n Tutkimussäätiö and the Ulla Tuominen Foundation.

I would like to acknowledge all my colleagues at the IT department. I am grateful to everyone who have co-authored papers with me which are included in this thesis. I am thankful to D.Sc. (Tech) Ethiopia Nigussie, D.Sc. (Tech) Liang Guang and D.Sc. (Tech) Thomas Canhao Xu for proof-reading part of this thesis. Associate Professor Pasi Liljeberg deserves special thanks for his guidance in last phase of the thesis in spite of his busy schedules. I am grateful to my colleagues Kameswar Rao Vaddina, Rajeev Kumar Kanth, and Amir-Mohammad Rahmani for their time to have valueable discussions. I am very thankful TUCS and IT department management personnels especially Irmeli Laine, Tomi Mäntylä, Maria Prusila, and Late Maarit Pöyhönen.

I would like to express my deepest gratitude to my siblings for their constant support, encouragement and most importantly taking care of my responsibilities at home. I am also indebted to my brothers Tariq Mahmood Wains and Daoud Ahmad Wains, who always encouraged me to follow my

ambitions, irrespective of how much they missed me. I am grateful to my friends Ahmad Tariq and Abdul Samad from Tampere, Nauman Khan and Ali Shuja for their nice company in Turku, and Adnan Ahmed, Sulman Mahmood and Ganguly Debashish for spending nice time with them during my stay in Stockholm.

Turku, November 2013 Khalid Latif

## Contents

| 1        | Inti | coduction                                                  | 1  |

|----------|------|------------------------------------------------------------|----|

|          | 1.1  | Driving Forces for Parallel Computing                      | 2  |

|          |      | 1.1.1 Computation                                          | 2  |

|          |      | 1.1.2 Communication                                        | 3  |

|          |      | 1.1.3 Power Consumption                                    | 4  |

|          | 1.2  | Design Challenges of Parallel Embedded Systems             | 4  |

|          | 1.3  | Thesis Objectives and Contributions                        | 6  |

|          | 1.4  | Overview of the Thesis                                     | 8  |

|          | 1.5  | Research Publications                                      | 8  |

| <b>2</b> | Par  | allel MPSoC Architectures                                  | 11 |

|          | 2.1  | Segmented Bus Architecture                                 | 12 |

|          | 2.2  | Network-on-Chip                                            | 14 |

|          | 2.3  | Three Dimensional NoC (3D-NoC)                             | 18 |

|          | 2.4  | Chapter Summary                                            | 19 |

| 3        | Des  | sign Flow for SegBus Platform                              | 21 |

| _        | 3.1  | Existing Design Methodologies for On-Chip Communication    |    |

|          |      | Architectures                                              | 22 |

|          | 3.2  | Unified Design Methodology for Application and MPSoC plat- |    |

|          |      | form                                                       | 23 |

|          |      | 3.2.1 Tool Environment                                     | 23 |

|          |      | 3.2.2 Application Partitioning                             | 27 |

|          |      | 3.2.3 Code Generation                                      | 28 |

|          | 3.3  | Experimental Results                                       | 30 |

|          | 3.4  | Chapter Summary                                            | 31 |

| 4        | Cor  | ${f nmunication \ Services \ in \ } {f SegBus \ Platform}$ | 33 |

|          | 4.1  | Existing Communication Services for MPSoC Architectures .  | 35 |

|          | 4.2  | Development of Communication Services                      | 36 |

|          |      | 4.2.1 Scheduling                                           | 36 |

|          |      | 4.2.2 SPLIT Transactions                                   | 41 |

|          |      | 4.2.3 Interrupt Communication                              | 43 |

|          |      |                                                            |    |

|   |                | 4.2.4 Multicast Transactions                                | 44              |

|---|----------------|-------------------------------------------------------------|-----------------|

|   | 4.3            | Experimental Results                                        | 47              |

|   | 4.4            | Chapter Summary                                             | 48              |

| 5 | Imp            | proving Resource Utilization in NoCs                        | 49              |

|   | 5.1            | Existing Resource Utilization Techniques                    | 5(              |

|   |                | 5.1.1 Application Mapping Techniques                        | 5(              |

|   |                | 5.1.2 Buffer Management Techniques for Bandwidth Utiliza-   |                 |

|   |                | tion                                                        | 51              |

|   | 5.2            | Application Mapping for Minimal Routing                     | 52              |

|   |                | 5.2.1 Prioritization of IP Cores                            | 53              |

|   |                | 5.2.2 Placement (Platform Dependent)                        | 55              |

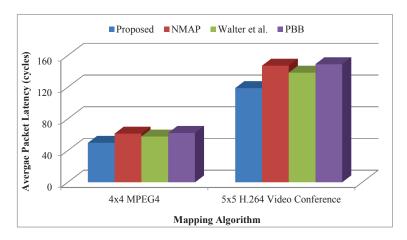

|   |                | 5.2.3 Simulation Results                                    | 56              |

|   | 5.3            | Channel Utilization                                         | 58              |

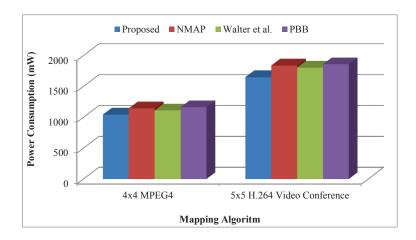

|   |                | 5.3.1 Synthetic Traffic Analysis                            | 59              |

|   | ٠,             | 5.3.2 Application Traffic Analysis                          | 62              |

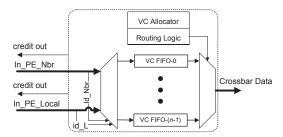

|   | 5.4            | Partial Virtual Channel Sharing (PVS) Router Architecture . | 64              |

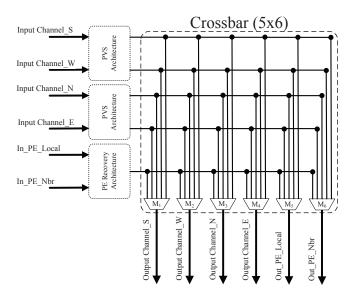

|   |                | 5.4.1 Virtual Channel Sharing Logic                         | 65              |

|   |                | 5.4.2 Crossbar Switch                                       | 68              |

|   |                | 5.4.3 Comparison with Existing Architectures                | 68              |

|   | 5.5            |                                                             | $\frac{69}{74}$ |

|   | 6.6            | Summary                                                     | 14              |

| 6 | $\mathbf{Net}$ | work Level Fault Tolerance in PVS-NoC Architecture          | 75              |

|   | 6.1            | Existing Fault Tolerance Techniques                         | 75              |

|   | 6.2            | Fault Scenarios                                             | 7               |

|   | 6.3            | Performance Sustainability under Faults                     | 80              |

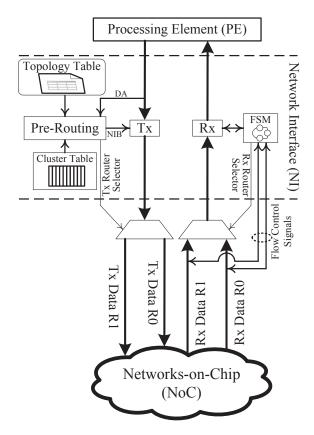

|   | 6.4            | Network Interface Assisted Pre-Routing                      | 86              |

|   |                | 6.4.1 Addressing Scheme                                     | 87              |

|   |                | 6.4.2 Control Logic for Packet Reception                    | 88              |

|   | 6.5            | Simulation Results                                          | 90              |

|   |                | 6.5.1 Performance Sustainability under Link Faults          | 90              |

|   |                | 6.5.2 Fault Tolerance for Routing Logic                     | 92              |

|   |                | 6.5.3 Reduction in Average Packet Latency by Network In-    | 0.6             |

|   | c c            | terface Assisted Routing                                    | 93              |

|   | 6.6            | Summary                                                     | 96              |

| 7 |                | aptiveZ Routing for 3D NoC-Bus Hybrid Architectures         | 97              |

|   | 7.1            | Motivation and Contribution                                 | 98              |

|   | 7.2            | Proposed Architecture                                       | 99              |

|   | 7.3            | v e                                                         | $10^{2}$        |

|   | 7.4            |                                                             | 105             |

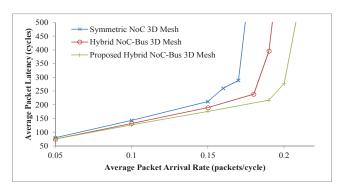

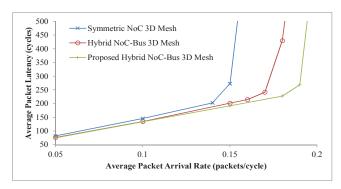

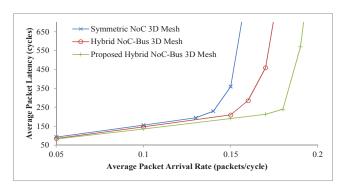

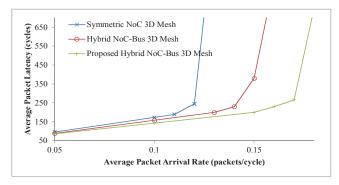

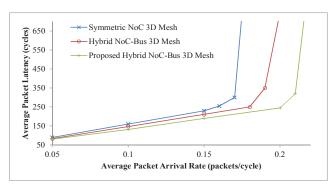

|   |                | 7.4.1 Synthetic Traffic Analysis                            | 105             |

|     | Elusions 1                        |     |

|-----|-----------------------------------|-----|

| 7.5 | Summary                           | .09 |

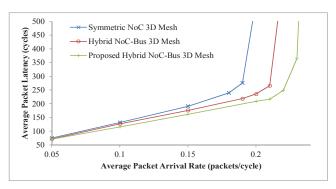

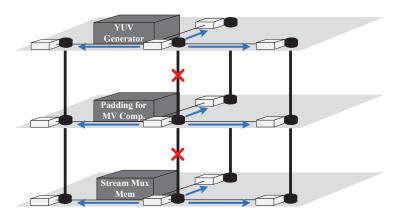

|     | 7.4.2 Videoconference Application | .06 |

# List of Figures

| 1.1  | Evolution of on-chip communication architectures as a commercial product | 3  |

|------|--------------------------------------------------------------------------|----|

| 2.1  | Design flow for Parallel MPSoCs [115]                                    | 12 |

| 2.2  | Segmented bus structure                                                  | 13 |

| 2.3  | The data packet structure and the flow of an inter-segment               |    |

|      | packet transfer                                                          | 14 |

| 2.4  | Abstraction between computation and communication                        | 14 |

| 2.5  | Homogeneous 4×4 NoC with Mesh Topology                                   | 15 |

| 2.6  | Typical Virtual Channel Router Architecture [109]                        | 17 |

| 2.7  | 3D Symmetric Mesh NoC structure                                          | 18 |

| 3.1  | H.264 Encoder                                                            | 24 |

| 3.2  | Unified Design Process for Application and MPSoC platform                | 25 |

| 3.3  | The H.264 Video encoder application model                                | 26 |

| 3.4  | The communication matrix for the example                                 | 27 |

| 3.5  | PSDF application specification                                           | 28 |

| 3.6  | The structure of the programme line, with two examples                   | 30 |

| 4.1  | Classification of on-chip services.                                      | 34 |

| 4.2  | Segbus Design Methodology                                                | 37 |

| 4.3  | Segbus scheduler structure.                                              | 38 |

| 4.4  | Task graph                                                               | 39 |

| 4.5  | Single bus scheduling                                                    | 39 |

| 4.6  | Two segment $SegBus$ scheduling                                          | 39 |

| 4.7  | Program line example, with parameters: $max\_dest=3$ , $max\_segs$       | =3 |

|      | $max\_enable{=}4. \dots \dots \dots \dots \dots$                         | 40 |

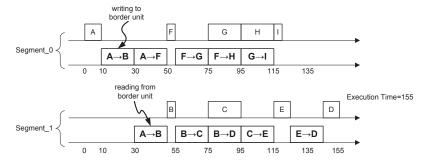

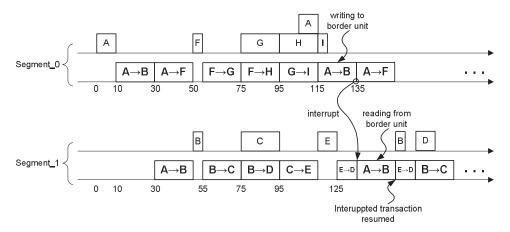

| 4.8  | Inter Segment transfer control                                           | 42 |

| 4.9  | Interrupt scheduling                                                     | 44 |

| 4.10 | Packet read mechanism.                                                   | 46 |

| 4.11 | Packet Format                                                            | 46 |

| 4.12 | Packet read mechanism                                                    | 47 |

| 5.1  | Packet Traversal Mechanism for Buffered NoC Architectures.               | 50 |

| 5.2  | Example application mapping with limited availability of cores.      | 53  |

|------|----------------------------------------------------------------------|-----|

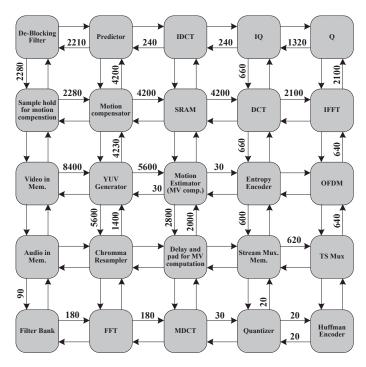

| 5.3  | Video conference encoder (VCE) application                           | 54  |

| 5.4  | Mapping generated for the VCE application                            | 58  |

| 5.5  | Average Packet Latency with XY routing algorithm                     | 59  |

| 5.6  | Power consumption with XY routing algorithm                          | 59  |

| 5.7  | Traffic load analysis for XY-routing.                                | 61  |

| 5.8  | MPEG4 application [102]                                              | 63  |

| 5.9  | Data transmission format.                                            | 65  |

| 5.10 | Proposed PVS approach for conventional Virtual Channel Ar-           |     |

|      | chitecture                                                           | 66  |

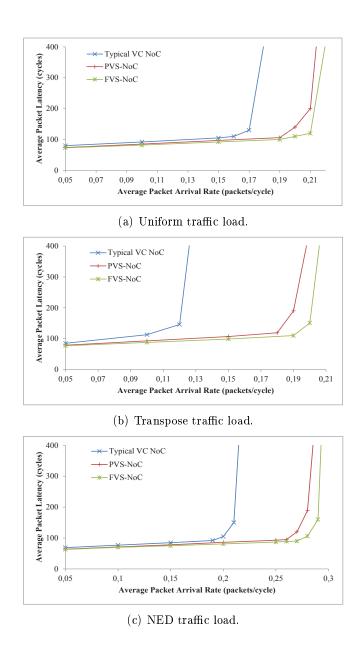

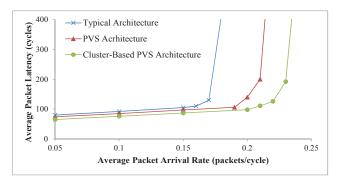

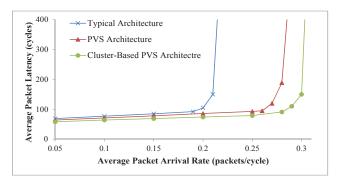

| 5.11 | Average Packet Latency vs. Packet injection rate for 5×5             |     |

|      | Mesh 2D NoC with (2, 2, 1) combination of PVS approach.              | 71  |

| 5.12 | VCE application mapped to $3\times3\times3$ 3D-Mesh NoC              | 72  |

| 6.1  | Routing in presence of faulty links                                  | 78  |

| 6.2  | Typical Virtual Channel Input Port Architecture                      | 79  |

| 6.3  | Resource utilization under faults by PVS approach                    | 80  |

| 6.4  | Load management in PVS approach under faults on VC buffers.          | 81  |

| 6.5  | Impact of faulty routing logic on routing                            | 82  |

| 6.6  | Routing logic fault tolerance by PVS approach                        | 82  |

| 6.7  | Resource reclamation by PVS approach under faults                    | 83  |

| 6.8  | PE Recovery architecture                                             | 84  |

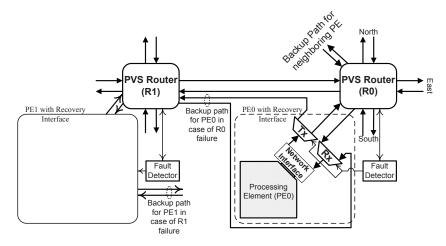

| 6.9  | PE Recovery Router                                                   | 85  |

| 6.10 | PE recovery architecture with dual inputs and single output.         | 85  |

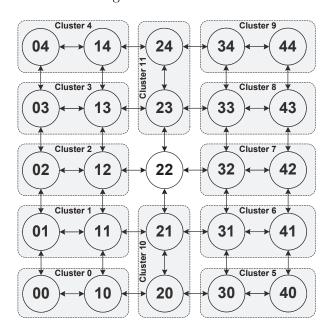

| 6.11 | Clustering of 6×6 NoC for NI assisted pre-routing                    | 86  |

| 6.12 | Network Interface architecture for pre-routing of packets            | 88  |

| 6.13 | Finite state machine for the proposed control logic for packet       |     |

|      | reception of PE0 in Figure 6.8                                       | 89  |

| 6.14 | $5 \times 5$ 2D-Mesh NoC with two faulty links                       | 90  |

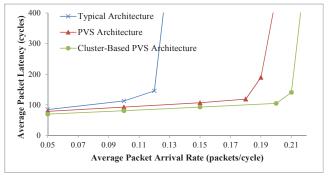

| 6.15 | Average Packet Latency vs. Packet injection rate for $5 \times 5$    |     |

|      | Mesh 2D NoC with (2, 2, 1) combination of PVS approach               | 91  |

| 6.16 | $6\times6$ 2D-Mesh NoC with faulty routing logics                    | 92  |

| 6.17 | Average Packet Latency vs. Packet injection rate for $6 \times 6$    |     |

|      | Mesh 2D NoC with fault on routing logics shown in Figure             |     |

|      | 6.16(a)                                                              | 93  |

| 6.18 | Clustering of $5 \times 5$ 2D Mesh NoC for simulation of NI assisted |     |

|      | pre-routing                                                          | 94  |

| 6.19 | Simulation curves for average packet latency (APL) vs. packet        |     |

|      | injection rate for $5\times5$ Mesh 2D NoC with $(2,2,1)$ combination |     |

|      | of PVS approach                                                      | 95  |

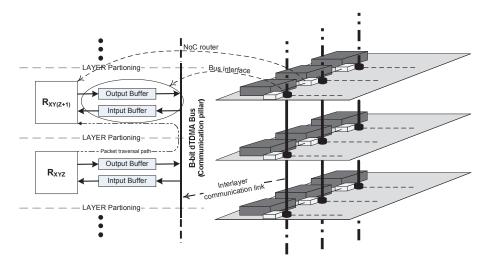

| 7.1  | Side view of the 3D NoC with the dTDMA bus                           | 98  |

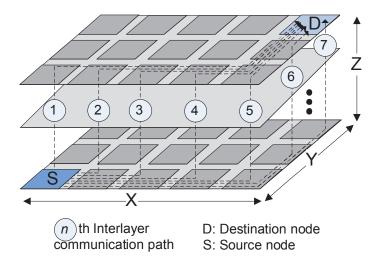

| 7.2  | Example of $AdaptiveZ$ routing                                       | 100 |

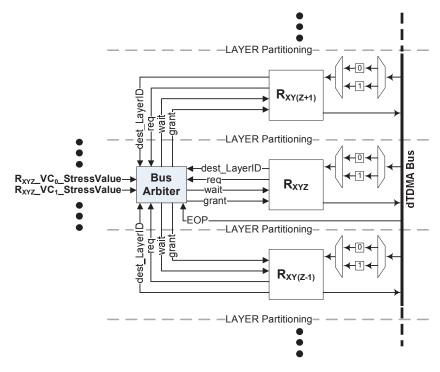

| 7.3 | VC architecture for the stacked mesh architecture                        | 102 |

|-----|--------------------------------------------------------------------------|-----|

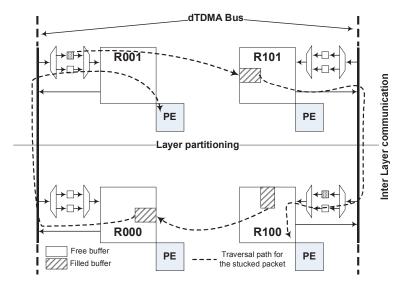

| 7.4 | Side view of the proposed stacked mesh architecture                      | 103 |

| 7.5 | Example of modifications to the proposed routing algorithm               |     |

|     | to guarantee single bus-link failure tolerance                           | 104 |

| 7.6 | Latency versus average packet arrival rate for a $3\times3\times3$ NoC . | 106 |

| 7.7 | Latency versus average packet arrival rate for a $3\times3\times4$ NoC . | 107 |

| 7.8 | 3D NoC running the video conference encoding application                 |     |

|     | with one faulty bus                                                      | 108 |

## List of Tables

| 3.1 | The task allocation and associated cost results                                                 | 27  |

|-----|-------------------------------------------------------------------------------------------------|-----|

| 4.1 | Communication cost with and without multicast service for H.264 application with three segments | 48  |

| 4.2 | Platform power consumption with and without Multicast ser-                                      |     |

|     | vice                                                                                            | 48  |

| 5.1 | Comparison with existing NoC router architectures                                               | 69  |

| 5.2 | Experimental results for VCE application, mapped to $3\times3\times3$                           |     |

|     | 3D-Mesh NoC                                                                                     | 73  |

| 5.3 | Experimental results for VCE application, mapped to $5 \times 5$                                |     |

|     | 2D-Mesh NoC, shown in Figure 5.4                                                                | 73  |

| 5.4 | PVS-NoC router Silicon Area for different grouping combina-                                     |     |

|     | tions                                                                                           | 74  |

| 6.1 | Silicon area of the existing and proposed NoC router architec-                                  |     |

|     | tures                                                                                           | 96  |

| 7.1 | Power Consumption and Average Packet Latency                                                    | 108 |

| 7.2 | Power Consumption and Average Packet Latency                                                    |     |

|     |                                                                                                 |     |

## List of Abbreviations

APL Average Packet Latency

APAR Average Packet Arrival Rate

BiNoC Bidirectional NoC

BIST Built In Self Test

**BU** Border Unit

**CA** Central Arbitration Unit

CMOS Complementary Metal Oxide Semiconductor

CRC Cyclic Redundancy Check

**DCS** Dual Connected mesh Structure

**DSB** Distributed Shared Buffer

**ECC** Error Correction Code

**ERAVC** Enhanced Reliability Aware Virtual Channel architecture

**FLOPS** FLoating-point Operations Per Second

**FU** Functional Unit

**FVS** Full Virtual channel Sharing

GALS Globally Asynchronous Locally Synchronous

GDS Graphic Database System

IC Integrated Circuit

IP Intellectual Property

NI Network Interface

MPSoC MultiProcessor System-on-Chip

NoC Network-on-Chip

**OFDM** Orthogonal Frequency-Division Multiplexing

PE Processing Element

**PSDF** Packet SDF

PVS Partial Virtual channel Sharing

SA Segment Arbitration unit

**SDF** Synchronous Data Flow

SegBus Segmented Bus

**SoC** System-on-Chip

TSV Through-Silicon Via

UML Unified Modeling Language

VC Virtual Channel

## Chapter 1

## Introduction

Ever-increasing performance and reliability requirements on electronic systems are the key driving factors for evolution of the integrated circuit technology. These applications can be categorized as computation intensive and data intensive [19,20]. Computation intensive applications require the computational elements with high processing power. On the other hand, data intensive applications are designed for working with large data-sets which require high bandwidth for inter-component data communications. In short, each type of application has its own requirements on processing and inter component communication hardware. Thus the conventional high performance computing platforms are not enough to fulfill the requirements of modern applications.

Buses and point to point connections are attractive solutions for on-chip communications with limited bandwidth requirements and smaller number of connected components. The bandwidth provided by bus can be effectively utilized because it is shared by several communication partners. However as the constant scaling of CMOS technology enabled integration of more computation components onto a single die, the bandwidth provided by on-chip buses was not scalable to higher number of integrated computation components [76]. Other than bandwidth limitations, power consumption because of high capacitive load due to long interconnection wires makes it inefficient to use the on-chip buses for larger number of components. As a consequence, segmented bus (SegBus) [63] and hierarchical bus [2] were proposed to deal with the mentioned issues. Once the number of connected components exceeded the certain limit, bandwidth limitations became a major bottleneck again. As a result, Network-on-Chip (NoC) [122], and Three dimensional NoC (3D-NoC) [3] platforms were proposed which have the potential to meet the scalability requirements.

Though the main task of efficient computing systems is to minimize the task completion time but power consumption, cost, and design time are also

the key parameters, which are leading the integrated circuit technology road map from single-core to multi- and many-core systems. Enormously parallel processing has become a mainstream and promising computing platform for high performance computing solutions with reduced power consumption [1]. To get full benefit of parallel processing, a multiprocessors system needs an efficient on-chip communication architecture [76, 108]. This thesis presents the scalability issues for on-chip interconnection platforms using novel system level optimization techniques for fault tolerance, power consumption and throughput performance.

#### 1.1 Driving Forces for Parallel Computing

Almost a decade ago, Intel abandoned the plan of high clock rates and started putting multiple processing cores on a single chip because of severe heat problems [4]. Until that time, increasing the clock rate showed direct and positive impact on software performance without any change in software code. But this technological paradigm shift changed the basic principle of software programming to evaluate the application's performance. Only the applications, which can be redesigned in an efficient way to run parallel tasks on different cores can be benefited form this fundamental change.

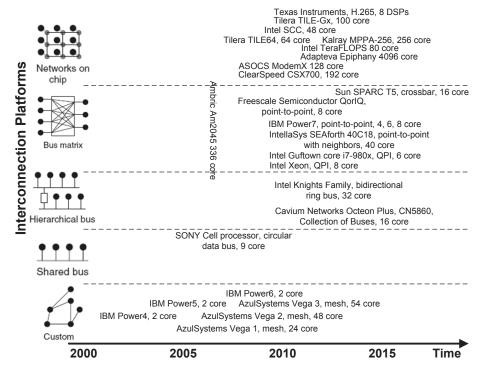

The very first challenge after switching to multi-core systems was to provide an efficient interconnection platform for on-chip communications among different cores. Different on-chip communication platforms have been proposed, such as bus, hierarchical bus, bus matrix (crossbar), networks-on-chip (NoC) or customized application-specific architectures. Each platform has its own pros and cons. The evolution of on-chip communication architectures with time and when different manufacturers commercially manufactured them is shown in Figure 1.1. There are different driving forces which motivated the designers to switch from sequential to parallel computing. Few of those have been discussed here.

#### 1.1.1 Computation

To meet the computation requirements of modern applications like multimedia signal processing, cloud based servers, satellites generating massive amounts of data or analyzing other larger scientific data-sets, parallel and distributed computing became the major focus of research community in computer science and engineering. Accordingly, high performance computing systems were commercially manufactured in recent years as can be seen in Figure 1.1. For instance, H.265 video codec recently manufactured by Texas Instruments [5], an 8-core digital signal processor at 1.25 GHz achieves 160 GFLOPS (160 × 10<sup>9</sup> floating-point operations per second). TILE64 processor manufactured by Tilera in 2007 [7], a 64-core processor is able to

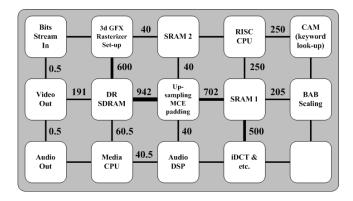

Figure 1.1: Evolution of on-chip communication architectures as a commercial product.

execute 166 billion 32-bit operations per second at 866 MHz. The Gulftown score i7-980X processor manufactured by Intel in 2010 [6], a 6-core processor at 3.33 GHz can achieve 79.992 GFLOPS. The Knights Ferry processor manufactured by Intel in 2010 [6], is a 32-core processors, which can exceed 750 GFLOPS at 1.2 GHz. The TeraFLOPS manufactured by Intel in 2011 [6], an 80-core processor at 3.16 GHz can achieve over 1.0 TFLOPS. Thus there is a pool of multi-core systems, where each system contains massive computing power. Now, it is up to the designer to select the appropriate hardware according the application requirements.

#### 1.1.2 Communication

After having many cores with massive computation capability, the next issue is the inter core communication. Multi-core systems use different platforms for on-chip communications, which manifest various features and provide different levels of bandwidth. It is the task of the application designer to select the platforms which provide high bandwidth for the applications requiring high rates of data transfers between different cores.

The H.265 codec, TILE64 and TeraFLOPS processors use NoC platform

for on chip communications and provide 2 Tbps, 2660 Gbps and 1.62 Tbps bisection bandwidth respectively. Gulftown processor uses QuickPath Interconnect (QPI) which is a point-to-point processor interconnect developed by Intel and provides 409.6 Gbps bandwidth for on-chip communications. The Knights Ferry processor uses the bi-directional ring bus for on-chip communications which can achieve the bandwidth of 307.2 Gbps). All these bandwidth values are reported for the same operating frequencies, mentioned in section 1.1.1.

#### 1.1.3 Power Consumption

Integrating a lot of computation and communication resources can make the system capable to meet the modern application requirements. However an efficient system should meet these requirements with minimum power consumption. The purpose of minimizing the power consumption of a chip is not only to save power but to minimize noise, timing contention, clock skew and chip temperature. This subsequently decreases the cost of cooling and packaging design, maximizes system reliability, simplifies power supply circuitry design, and increases battery lifetime [8]. At the same frequencies, mentioned in section 1.1.1, TeraFLOPS, H.265 codec, Gulftown and Knights Ferry processors consume 62 W, 7.5 W (at 75 °C, 9.5 W at 105 °C), 130 W TDP and 300 W TDP respectively. The thermal design power (TDP) refers to the maximum amount of power the cooling system in a computer is required to dissipate to prevent overheating. TILE64 processor consumes 60.8 W at 700 MHz operating frequency.

After having the detailed analysis and comparison of different multi-core systems from computation capability, communication bandwidth and power consumption perspectives, the target hardware should be selected according to the application requirements.

# 1.2 Design Challenges of Parallel Embedded Systems

On-chip communication architectures can be evaluated in terms of overheads and communication bandwidth availability [115]. The overheads are measured as silicon area, energy and power consumption. In order to meet high performance requirements, the communication architecture needs massive number of wires and complex control logic which cost in terms of a much larger power consumption and area overhead. The designer should ensure while selecting the communication architecture that the performance requirements are satisfied without violating the area and power consumption constraints. The second and major parameter to evaluate performance

of communication architecture is the value of supported bandwidth. For this purpose, design space exploration of communication architectures is necessary. In order to narrow down the design solution from a large set of design choices (topologies, control logics, application mapping techniques, traffic routing algorithms, and inter-core communication protocols are possible within the same architecture model), efficient design space exploration is critical to the shortening of time-to-market.

To evaluate the overheads and bandwidth of a distributed system, scalability is a primary metric. According to [9], scalability of distributed systems has three dimensions: numerical, geographical, and administrative. The numerical scalability represents the ability of the system to integrate an increasing number of components. The geographical scalability means the distance, over which the system components are scattered. The administrative dimension of scalability represents the administrative convenience with sizable system. The geographical scalability is extraneous for on-chip parallel systems and thus beyond the scope of this thesis. On the basis of design constraints and scalability dimensions, [10] has defined three aspects of scalability of on-chip parallel systems: Performance, Overhead and Design effort.

The performance metrics for any computing system are task completion time, on-chip communication latency, system throughput, and resource utilization. While switching to a parallel processing system from a single processor system, the basic parameter to evaluate the performance scalability is the speedup [11]. The speedup factor of multiprocessor systems is limited by application characteristics [12]. With advent of various on-chip communication platforms for parallel systems, the communication architecture has great impact on the speedup as well [115]. Thus collectively, there are several factors which limit the speedup factor like inter-core communication time, additional computations in parallel programmes and idle time slots for processors due to data dependencies on other processing elements.

All the mentioned issues for performance scalability can be dealt with at the expense of different overheads like silicon area and power consumption. Thus achieving speedup beyond the requirement without considering overheads is not an economical solution. An ideal solution should have better performance with minimum overheads. The silicon area has been the primary concern for chip designers. With continuous scaling of transistor size, silicon area became an exponentially cheaper resource relative to power and energy consumption [13]. Thus, the power consumption has replaced area as the primary constraint for SoC design. For smaller number of cores and lower bandwidth requirements, bus based communication is an efficient solution due to minimal communication overheads compared to NoC. On the other hand, bus based system does not scale well with more number of PEs because of the power consumption due to higher capacitive loads.

The last few decades were characterized by revolutions in information and communication technology. To cope with this ever changing revolution in our daily lives, never-ending update is required [14]. In this case, accelerating the time to market plays a vital role in product success. Generally, scalability in terms of design effort becomes a bottleneck to achieve this objective [15]. The design effort normally scales with number of integrated components. This design effort can be minimized by using techniques like reusability, early error detection and orthogonalization [16]. This minimizes the time for design and development process.

Another dimension, which affects system scalability is reliability. In conventional computing architectures, fault on a component makes the connected fault-free components inoperative. In such situations, the only drawback is not only the performance degradation. These affected fault-free components consume power as well. In modern systems, due to aggressive technology scaling, the probability of transient and permanent faults is increasing because of increased process variation and reduced noise-margins. Thus fault occurrence can severely and unexpectedly degrade the system performance. To deal with system reliability issues, fault detection should migrate to fault prediction [17]. It will reduce the number of unscheduled system stalls and cycle wastes. The main problem to switch from detection to prediction is to build precise, robust, power efficient, real-time updateable, and generic models for prediction. Another approach to retain the system performance in case of fault occurrence is to utilize the fault-free components which cannot be used due to the faults on the other resources.

Unfortunately, a system that is scalable in one or more scalability dimensions may cost in other scalability dimensions [18]. For the selection of on-chip communication platform, the application requirements should be considered with scalability issues.

### 1.3 Thesis Objectives and Contributions

A shift from computation centric design methodologies to communication centric design methodologies became essential in modern parallel systems [21]. Consequently, the design space exploration for on on-chip communication architectures is crucial. This thesis addresses the selection of on-chip communication platforms with an optimal tradeoff between system performance, reliability and overheads according to the application requirements and design constraints. To achieve this goal, different on-chip communication architectures and communication services have been proposed and evaluated regarding the computation performance, power consumption, silicon area and fault tolerance. The main contributions of this thesis are:

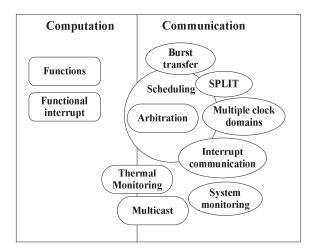

• The design flow for segmented bus (SegBus) platform including the

communication services is proposed. Different communication services like multicast, interrupt and split are introduced in SegBus platform. H.264 video encoder is used to demonstrate the proposed services. The designer can select the services according to the application and performance requirements.

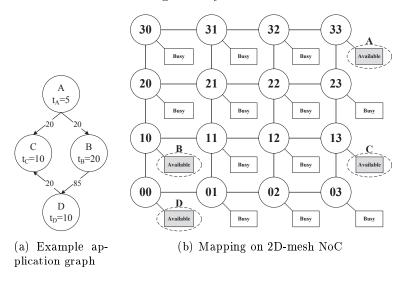

- Application mapping technique for Multiprocessor System-on-Chip (MP-SoC) platforms with homogeneous processing nodes is proposed. For this purpose, task prioritization criteria is proposed, which is used to map the application on MPSoC platform. NoC is used as a case study to compare the application mapping performance with existing task allocation techniques. The proposed technique shows significant improvement in system performance and reduction in power consumption.

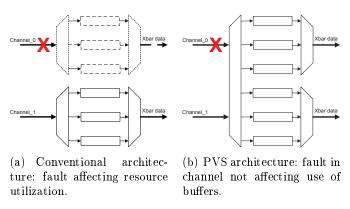

- A novel Partial Virtual channel Sharing (PVS) NoC architecture is proposed which improves the utilization of resources to enhance the performance with minimal overheads. The PVS-NoC architecture also reduces the impacts of faults on performance and tolerates the faults in routing logic. The runtime allocation of the buffers depends on incoming load and fault occurrence. Furthermore, an efficient and reliable Network Interface (NI) assisted routing strategy for NoC using PVS architecture is proposed. For this purpose, NoC system is divided into clusters. Each Processing Elements (PE) can inject data to the network through a router in the cluster, which is closer to the destination node. The proposed architecture can also recover the PE disconnected from the network due to network level faults by allowing the PE to transmit and receive the packets through other routers in the cluster. Simulation results reveal that PVS architecture improves the performance significantly in presence of faults, compared to other virtual channel (VC) based NoC architectures.

- An efficient architecture to optimize system performance, reduce power consumption, and enhance reliability of stacked mesh 3D NoC is proposed. For this purpose, an inter-layer communication mechanism is developed which addresses the load balancing and system fault-tolerance issues by enhancing the buffer utilization. Overall, the performance is enhanced by an adaptive inter-layer routing scheme called AdaptiveZ. For the sake of simplicity and to observe the contribution of AdaptiveZ in performance improvement, intra-layer communication uses static XY routing algorithm. Our extensive experiments show significant reduction in power consumption and average packet latency as compared to the typical stacked mesh 3D NoC architectures.

#### 1.4 Overview of the Thesis

The rest of the thesis is organized as follows. Chapter 2 presents the concept of on-chip communications for multi-core architectures and its main design choices like bus and network based architectures have been addressed. Chapter 3 describes the unified design methodology for application and MPSoC platform. SegBusplatform has been used as an example MPSoC architecture. To improve the system performance and resource utilization, communication services like multicast, interrupt communication and SPLIT transactions for SegBusplatform have been introduced in Chapter 4. To enhance the resource utilization in NoC based architectures, an application mapping technique has been presented in Chapter 5. Furthermore, the resource utilization analysis has been presented as well. On the basis of resource utilization analysis, Partial Virtual channel Sharing NoC (PVS-NoC) architecture has been proposed to address the utilization of virtual channel buffers in NoC router. Different techniques to reduce the impact of faults on system performance have been discussed in Chapter 6. Chapter 7 presents the adaptive inter layer communication mechanism for 3D NoC-Bus hybrid architectures to enhance the system performance and reduce the overall power consumption. Chapter 8 concludes the dissertation.

#### 1.5 Research Publications

The work discussed in this thesis is based on and extended from the international journals and proceedings of conferences listed below:

- 1. Khalid Latif, Ethiopia Nigussie, Tiberiu Seceleanu. Unified Prioritization Criteria for Application Mapping on MPSoC Platforms. Submitted to ACM Transactions on Embedded Computing Systems (TECS). Author's contributions: The author contributed with the problem formulation, conducted experiments and wrote the manuscript.

- 2. Khalid Latif, Amir-Mohammad Rahmani, Ethiopia Nigussie, Tiberiu Seceleanu, Martin Radetzki, Hannu Tenhunen. Partial Virtual Channel Sharing: A Generic Methodology to Enhance Resource Management and Fault Tolerance in Networks-on-Chip. Journal of Electronic Testing: Theory and Applications (Springer-JETT), 29(3), pp 431-452, June 2013. DOI 10.1007s10836-013-5389-5

- Author's contributions: The author formulated the resource sharing technique to enhance the system performance and address the fault tolerance issues. The author also wrote the manuscript. Amir-Mohammad Rahmani performed the simulations.

- 3. Khalid Latif, Amir-Mohammad Rahmani, Tiberiu Seceleanu, Hannu Tenhunen. Cluster based Networks-on-Chip: An Efficient and Fault-Tolerant Architecture using Network Interface Assisted Routing. Accepted for publication in IGI-Global International Journal of Adaptive, Resilient and Autonomic Systems (IJARAS), 2013.

Author's contributions: The author formulated the network interface assisted routing technique to reduce the network load and wrote the manuscript.

- 4. Khalid Latif, Tiberiu Seceleanu, Cristina Seceleanu, Hannu Tenhunen. Service based communication for MPSoC platform-SegBus. Microprocessors and Microsystems, Elsevier, 35(7), pp. 643-655, October 2011. DOI 10.1016j.micpro.2011.06.006

Author's contributions: The author contributed with the problem formulation, conducted experiments and wrote the manuscript.

- 5. Amir-Mohammad Rahmani, Khalid Latif, Pasi Liljeberg, Juha Plosila, Hannu Tenhunen. A Stacked Mesh 3D NoC Architecture Enabling Congestion-Aware and Reliable Inter-Layer Communication. In proceedings of IEEE/Euromicro International Conference on Parallel, Distributed, and Network-Based Processing (PDP) in Special Session on On-Chip Parallel and Network-Based Systems, pp. 423-430, Ayia Napa, Cyprus, February 2011.

- Author's contributions: The author proposed the idea, suggested experimentation methods, and wrote the manuscript.

- 6. Khalid Latif, Amir-Mohammad Rahmani, Tiberiu Seceleanu and Hannu Tenhunen, "An Autonomic NoC Architecture using Heuristic Technique for Virtual Channel Sharing," in Phan Cong-Vinh (Eds.), Autonomic Networking-on-Chip: Bio-inspired Specification, Development, and Verification. Part of the Embedded Multi-core Systems (EMS) Book Series, CRC Press, December 2011. 1st Edition, pp. 47-68, ISBN: 143982911X, 9781439829110

Author's contributions: The author formulated the problem and wrote.

- Author's contributions: The author formulated the problem and wrote the manuscript.

- Khalid Latif, Amir-Mohammad Rahmani, Tiberiu Seceleanu, Hannu Tenhunen. Power- and Performance-Aware IP Mapping for NoC-Based MPSoC Platforms. In proceedings of IEEE International Conference on Electronics Circuits and Systems (ICECS), pp. 760-763, Athens, Greece, December 2010.

- Author's contributions: The author developed the mapping technique, conducted experiments and wrote the manuscript.

8. Khalid Latif, Moazzam Niazi, Hannu Tenhunen, Tiberiu Seceleanu, Sakir Sezer. Application development flow for on-chip distributed architectures. In proceedings of 21st IEEE International SoC Conference (SOCC), pp. 163-168, Newport Beach, CA, USA, September 2008. Author's contributions: The author proposed the application design flow for MPSoC, conducted experiments and wrote the manuscript.

## Chapter 2

## Parallel MPSoC Architectures

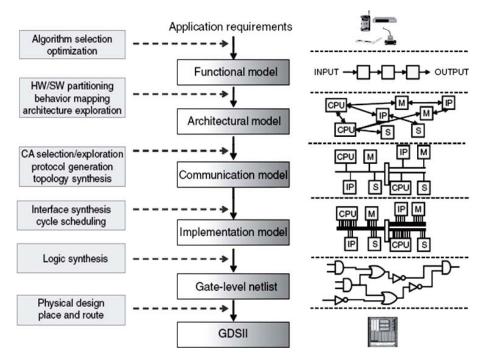

Multiprocessor System-on-Chip (MPSoC) addresses the never ending complexity of applications. Like a traditional SoC design flow, MPSoC design starts with application specifications and requirements as shown in Figure 2.1. After the application specification, a functional model can be formulated using system-level design tools like Simulink or high level language such as C/C++ to verify and optimize the application algorithm using different configurations and random as well as normal inputs. In next step, the implementation approach for each application task is decided. It is a decisive step for power, performance and area optimizations of computation units. The computation tasks implemented as a circuit are called hard components. These hard components can be implemented using different logic architectures like Programmable Logic Devices (PLD), General-Purpose Logic (GPL) devices, Field Programmable Gate Arrays (FPGA) or Application-Specific Integrated Circuit (ASIC). While rest of the tasks are implemented as a sequential set of instructions on a microprocessor which are called soft components. At this stage, application architecture model is available. All inter-node communication in architecture model use point-to-point (P2P) links.

For applications, where subset of cores communicates with most of the nodes in application, P2P based communication architecture can provide the best communication performance at the expense of silicon area and high power consumption [21]. At this stage, MPSoC design flow differs from traditional SoC design flow. An efficient architecture for inter-core communications with minimum overheads is required for MPSoC designs. MPSoC's performance is highly dependent on the selection of communication architectures [56]. The focus of this thesis is to facilitate the designer for communication platform selection in MPSOC designs. In this chapter, different on-chip communication platforms will be presented which provide the foundation for the rest of the thesis.

Figure 2.1: Design flow for Parallel MPSoCs [115].

#### 2.1 Segmented Bus Architecture

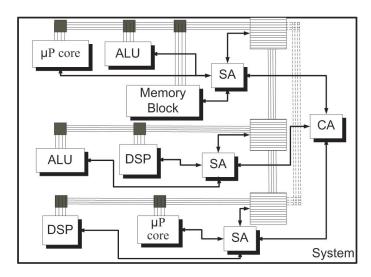

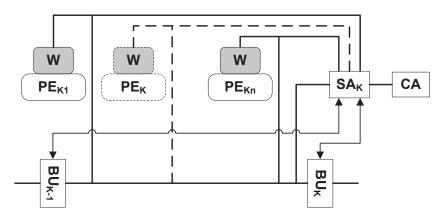

A segmented bus ( SegBus ) is a bus which is partitioned into two or more segments. Each segment acts as a normal bus between modules that are connected to it and operates in parallel with other segments. Neighboring segments can be dynamically connected to each other in order to establish a connection between modules located in different segments. Due to the segmentation of the bus, parallel transactions can take place, thus increasing the performance. A high level block diagram of the segmented bus system which we consider in the following sections is illustrated in Figure 2.2.

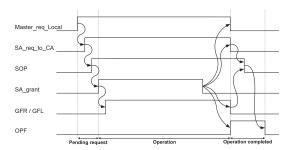

The SegBus platform [63] is thought as having a single central arbitration unit (**CA**) and several local segment arbitration units (**SA**), one for each segment. The **SA** of each bus segment decides which device, generically referred as functional unit (**FU**), within the segment will get access to the bus in the following transfer burst.

**Platform communication.** Within a segment, data transfers follow a "traditional" bus-based protocol, with **SA**s arbitrating the access to local resources. The inter-segment communication is a packet based, circuit switched approach, with the **CA** having the central role. The interface components between adjacent segments, the *border units* - **BU**s, are basically FIFO ele-

Figure 2.2: Segmented bus structure.

ments with some additional logic, controlled by the **CA**. A brief description of the communication is given as follows.

Whenever one **SA** recognizes that a request for data transfer targets a module outside its own segment, it forwards the request to the **CA**. This one identifies the target segment address and decides which segments need to be dynamically connected in order to establish a link between the initiating and targeted devices. When this connection is ready, the initiating device is granted the bus access. This one starts filling the buffer of the appropriate bridge with the packet data. The latter is taken into account by the corresponding next segment **SA** which forwards it further, until it reaches the destination. At this point, the **SA** of the targeted segment routes the packet to the own segment lines, from here it is collected by the targeted device.

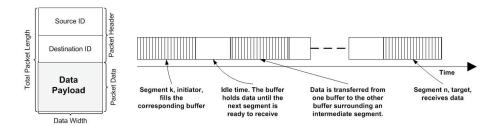

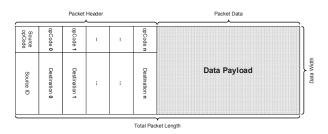

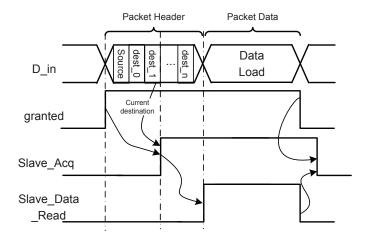

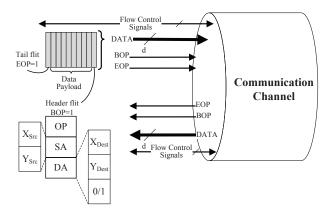

A transfer from the initiating segment k to the target segment n is represented in Figure 2.3. The packet structure shown in figure contains different fields. Destination ID field is the  $\mathbf{F}\mathbf{U}$ 's ID as packet destination. Similarly Source ID is the  $\mathbf{F}\mathbf{U}$ 's ID as packet source. Data payload is the actual data to be transferred. The segments from k to n are released for possible other inter-segment operations in a cascaded manner, from the source k to the destination, n as specified by the packet header. However, the figure stresses the relatively long duration of an inter-segment transfer: whenever the data has arrived in the  $\mathbf{B}\mathbf{U}$  FIFOs, such a transaction collides with ongoing local activities. A solution in this sense, that is, speeding up the global communication, comes in the form of interrupts [61]: when a data packet arrives at one  $\mathbf{B}\mathbf{U}$ , the local operations of the next segment to be traversed is interrupted, to make way for the inter-segment packet.

The arbitration at CA level, that is, for global transfers, implements

Figure 2.3: The data packet structure and the flow of an inter-segment packet transfer.

the application dataflow, with respect to these transfers. Hence, one has to implement accurate control procedures for inter-segment transfers, as possible conflicting requests must be appropriately satisfied, in order to reach performance requirements and to correctly implement applications.

The bus snooping mechanism is shown in Figure 2.4. Wrapper (**W**) provides the abstraction between processing elements (**PE**) and communication platform to make the system plug-and-play. Here, the task of the wrapper is requesting the bus, reading data from bus and other control signals communication. In packet based communication, packetization and depacketization are additional tasks of the wrapper.

Figure 2.4: Abstraction between computation and communication.

The SegBus platform specifics consist in a set of global parameters that have a great impact on the implementation [63]: (i) topology - a linear or circular geometry; (ii) number of segments; (iii) size of the data packet.

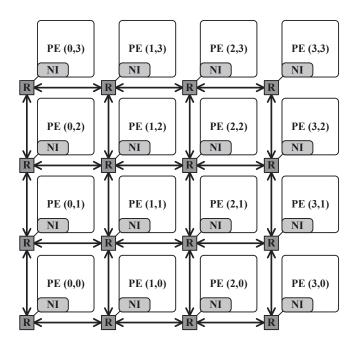

#### 2.2 Network-on-Chip

Network-on-Chip (NoC) is a general purpose on-chip communication concept which answers to the problems induced by wire density in SoCs and offers high throughput, which are the basic requirements to deal with complexity of modern systems [56,76,122]. It is an attractive solution to replace the conventional communication architectures such as shared buses or point-to-point dedicated links. NoC provides better scalability than on-chip buses because as more resources are introduced to a system, also more routers and links are introduced to connect them to the network. The additional links and routers fulfill the communication capacity requirements for new resources. A typical NoC based system consists of processing elements (PE), network interfaces (NI), routers (R) and inter-router communication channels as shown in Figure 2.5.

Figure 2.5: Homogeneous  $4\times4$  NoC with Mesh Topology.

The NoCs can be categorized as homogeneous and heterogeneous. Homogeneous NoCs are based on the replication of identical PE units, while heterogeneous NoCs are based on variety of PE cores. The PEs can be a general purpose processor core, a cache bank, a memory controller, an FPGA block or even a custom logic component. Generally, heterogeneous NoCs are more efficient than homogeneous ones. However, homogeneous NoCs provide better flexibility, fault tolerance and scalability [22]. PEs act as the source and sink for the information/data packets, inject to the network. In rest of the thesis, homogeneous NoCs are used to provide the better comparison of communication performances. Thus, all possible software procedures are mapped within the general purpose hardware devices.

In NoC based system, PEs communicate with each other by breaking

up a message into small packets for transmission. At destination node, the received packets are re-ordered to extract the real message. The network interface (NI) is the component which packetizes the data before injecting it to the network and de-packetizes the packet after it leaves the network but before delivering it to the destination PE [122]. The packetization/de-packetization provides abstraction between computation and communication and makes the system plug-and-play for heterogeneous PEs [108]. A well designed NI enables the PE to utilize the full bandwidth with minimum latency offered by the network.

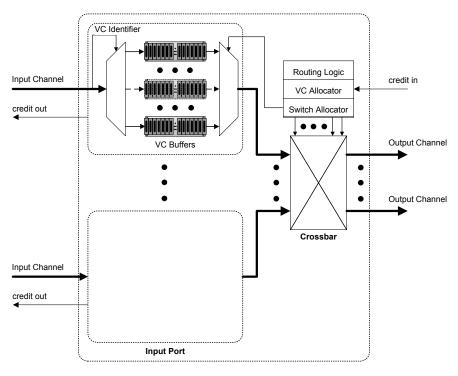

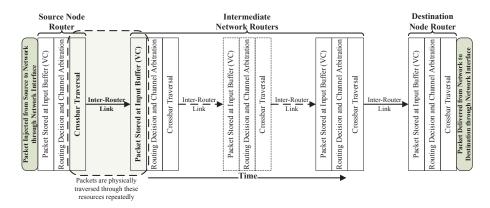

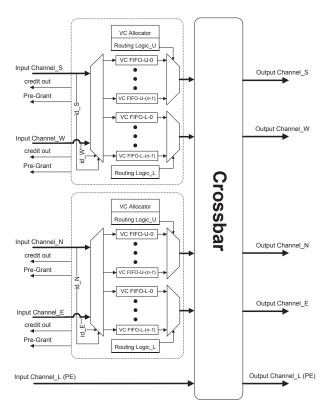

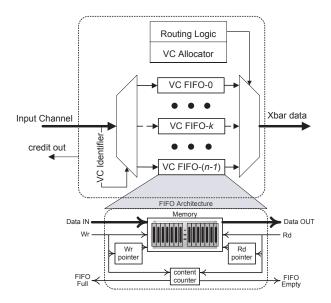

The task of the router (R) is to compute the route of the received packets and direct them towards the destination accordingly. These packets are received either from neighboring routers or the local PE. The router can be buffered or bufferless. For buffered routers, packets are stored in router buffers. The routing information is extracted from packet header flit and route is computed according to the implemented routing strategy. If the destination address of the packet matches with the address of local PE attached to the router, the packet is delivered the attached PE core, otherwise the packet is routed to the neighboring nodes according to the computed route. The concept of virtual channels has been introduced to address the utilization of communication channels and avoid deadlock. The VC based router contains a routing logic, a VC allocator, a switch allocator, a VC identifier, a crossbar switch, and several VC buffers and as shown in Figure 2.6. The number of IO channels for the router depends on topology. Different NoC router architectures like BiNoC [103], ViChar [114] and DSB-NoC [118] have been proposed which address different issues.

All inter-router communication channels in NoC can be simultaneously used for data transmission, which provides a high level of parallelism. Different interconnection design techniques and wire models can be used to design these channels. Similarly, variety of data encoding/decoding techniques and on-chip signaling schemes are available for data transmission on these links [23].

Other than mentioned hardware (HW) components, there are three other concepts which define NoC: Topology, Routing techniques and Flow control [122]. All these elements play an important role in determining the NoC performance. Network topology describes the the arrangements of routers and communication channels. Like the NoC concept, most of the proposed NoC topologies have been borrowed from computer networks or from network of multiple computation units in supercomputers. The main topology metrics are degree, hop count and path diversity. The well known NoC topologies are ring, mesh, torus, folded torus and tree structures (binary tree and fat tree).

The routing process decides, which path should be followed by a packet to reach its destination. A router can be defined as an ordered set of inter-router

Figure 2.6: Typical Virtual Channel Router Architecture [109].

communication channels. The routing information is inserted in header flit of the packet by NI during packetization. There are two basic types of routing: source routing and node-table routing [122]. In case of source routing, NI contains the routing table and complete route is defined and saved in packet header at the source node. On other hand, node-table routing uses distributed approach where each router is assigned an address and also contains the routing table. The route is computed at each router on the way of packet. In this case, only the destination address is included in packet header. Normally, deterministic and oblivious routing algorithms use source routing, while adaptive routing uses node-table routing to take advantage of network state information at intermediate hops along the route.

Flow control mechanisms in NoC manages the resource allocation for packets as they are traversed through the network. It also defines the granularity level of packet transfer. In a situation, when two packets are competing for the same resource, flow control mechanism resolves the conflict. For bufferless routers, flow control schemes like hot-potato have been defined. For routers with buffering capacity, flow control schemes like store-and-forward, virtual cut-through and wormhole routing have been defined.

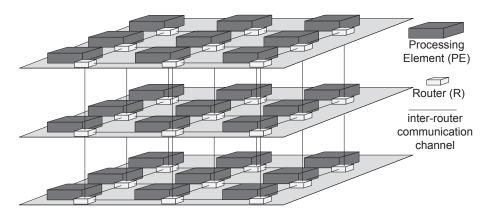

## 2.3 Three Dimensional NoC (3D-NoC)

A three-dimensional integrated circuit (3D-IC) is a major paradigm which can continue the Moore's law of integration [24]. 3D ICs offer a considerable reduction in the number and length of global interconnects as compared to traditional 2D ICs, which reduces wire delay and power consumption and enhances the system performance [25]. Due to all these benefits of 3D-ICs, the paradigm shift from 2D-NoC towards 3D-NoC was a very necessary step.

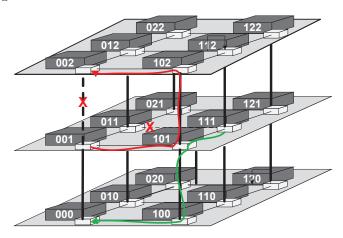

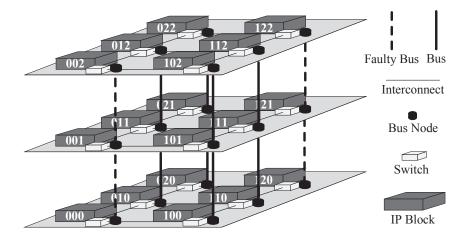

Different 3D-NoC architectures have been proposed [26], like Symmetric 3D Mesh, Ciliated 3D Mesh, Hybrid 3D NoC-Bus, True 3D NoC, Tree-Based 3D NoC and De-Bruijn Graph-Based 3D NoC. The simplest one for understanding is Symmetric 3D Mesh NoC. This approach is an extension of 2D mesh NoC, where in addition to existing links, each node has two additional links (up and down) for inter-layer communications. A  $3\times3\times3$  3D Symmetric Mesh NoC structure with 27 nodes is shown in Figure 2.7. For 3D Symmetric Mesh NoC structure, inter- or intra-layer hop bear the same characteristics at system level.

Figure 2.7: 3D Symmetric Mesh NoC structure.

The system performance of 3D Symmetric Mesh NoC structure is better than 2D Symmetric Mesh NoC because of two reasons: more communication resources (two extra ports for each router of 3D Symmetric Mesh NoC) and better bandwidth support by Through-Silicon-Vias (TSV) for inter-layer communications. TSV pads distributed across planar layers show relatively high area overheads. This may impose constraints on number of TSVs to avoid wire routing congestion [27]. Another drawback of 3D Symmetric Mesh NoC is the crossbar size. It requires a 7×7 router crossbar because of two extra links for inter-layer communications. It can be observed at a later stage from the simulation results that crossbar scales inefficiently due to increase of critical path length and extra gate count. To address all these issues and further enhance the performance of 3D-NoC structure, an efficient hybrid

3D NoC-Bus architecture and adaptive inter-layer routing scheme will be presented in Chapter 7.

With all the performance benefits, 3D technology introduces the on-chip thermal issue which increases the packaging and cooling costs. All these issues are faced by 3D-NoC architectures as well but it is beyond the scope of this thesis.

### 2.4 Chapter Summary

In this chapter, different parallel on-chip communication architectures have been presented which are the foundation for the next chapters. Different aspects and design issues of each platform like scalability, communication mechanism, bandwidth limitations and power consumption were discussed. The problems mentioned here have been addressed during the research work for this thesis. It is the task of the designer to select an appropriate interconnection platform according to the performance requirements and other design constraints such as power consumption for the application.

# Chapter 3

# Design Flow for SegBus Platform

One of the reasons behind the difficulties in MPSOC development is the lack of design methodologies [29]. Due to environmental and application requirements, the operation and communication characteristics of the employed devices and architectural instances may vary greatly from system to system. Performance measures are intrinsically related to the specifics of the underlying hardware platform. The lack of information availability at the higher abstraction (application) layers affects how specification requirements are reflected in the final system realization. Another important issue is the control of data transfers between different devices, as concurrent communication will certainly create conflicting situations.

At the same time, there is a growing demand for performance of multimedia applications. In order to address such issue, both performant platforms, but as well efficient design methodologies need to be developed. Employment of Intellectual Property (IP) designs is one of the high requirements in order to allow a fast deployment of new design solutions. Alternatively, hardware design languages might prove at times to be too restrictive, as only a small part of the design community has good respective knowledge. The tendency is therefore to replace, or to make transparent, whenever possible, VHDL (for instance) based design with higher level constructs, for instance C-like languages. The new challenges reside now in having a good platform representation at these higher levels, such that early evaluations are possible to perform.

The present work delves into aspects related to design methodologies for MPSOC. We describe the principles of a stepwise design methodology that targets a distributed on-chip architecture, Segmented Bus (SegBus) platform [63]. We continue the work of previous research results in the direction of raising the levels of abstraction at which such methodology is beneficial.

We also take a step further in the direction of automation, by providing platform models in the framework offered by Matlab [79]. We are interested in Matlab/Simulink as a high level design environment which allows the exploration of allocation results and offers the possibility for early assessment of application - platform mapping.

The most common current methods to deal with concurrency are threads, semaphores, mutual exclusion locks, etc. However, these approaches are intended to build virtual parallel environments, most often not well suited for current heterogeneous multi processor systems. For instance, threads are defined as sequential processes, exchanging information through shared memory resources, and several synchronization methods must be implemented in order the ensure the security and reliability of the shared data. This is because threads are highly non-deterministic, and a immense effort is dedicated to establishing an order of execution.

Our approach here is based on the existence of segment and central arbiters that contain the schedule for data exchanges between devices within the same segment, or in different ones. Out of a possible group of "enabled" transfers, these devices select the appropriate one with a built-in policy of granting. The present study builds on the work of Truscan et. al [39], and it provides an improved tooling support for the development of applications.

# 3.1 Existing Design Methodologies for On-Chip Communication Architectures

In recent years, research started to address on-chip solutions. Different onchip communication architectures can use different design methodologies. Here we discuss the alternative design approaches for bus based on-chip communication architectures.

Lahiri et al. [33] address design optimality for a segmented bus platform similar to the SegBus. The segmented bus architecture [33] is, however, memoryless, different to our case, where the segments are separated by storage devices. Moreover, the protocols are fit to one application, and contentions can be extracted following a higher level simulation. The approach introduces a valuable simulation-based trace extraction, to indicate the communication patterns, considered consistent, after which an algorithmic solution is found to the allocation problem. Arbitration issues are not specifically addressed, and hence, possible contention problems and precedence relations are not analyzed. The intermediate arbitration tables, in our case, solve both the contention and the precedence issues.

Srinivasan et al. [37] introduce an AMBA-like hierarchy of a segmented bus. The authors employ genetic algorithms for finding optimal segmented bus allocations, but the methodology is not continued to other levels of abstraction. There is a similarity with [33], in the sense that no control procedures, either for local or inter-segment activities, is presented. The arbitration is possibly organized following AMBA protocols, but this may affect both allocation optimality and solving the conflicting task execution.

De Jong [32] elaborates a system design flow based on UML and SDL, mainly for the purpose of control, communication and synchronization refinement of both hardware and software components. As it pertains more to the area of software-hardware co-design, this study is viewed as a complementary research to the present work.

Dekeyser et al. [31] propose a "Y-chart" methodological approach to multiple SOC system design with UML. While the results are applicable to our specific platform-based approach, in general, several design steps, such as application and platform refinement, granularity, communication restrictions, are not captured in [31].

The approach we illustrate here does not impose restrictions towards other MPSOC platforms. For example, the existing network-on-chip [76] models like [40,41] can be used in order to enlarge the basis of the solution. Considered together with earlier results [39] on high level design methodologies, we approach the realization of a complete framework for the design of multiprocessor systems which provides the unified representation of both interconnection platform and application.

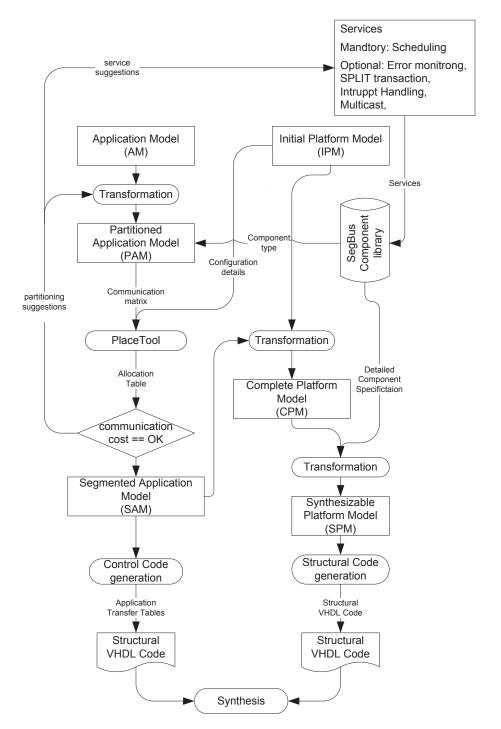

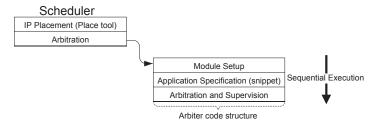

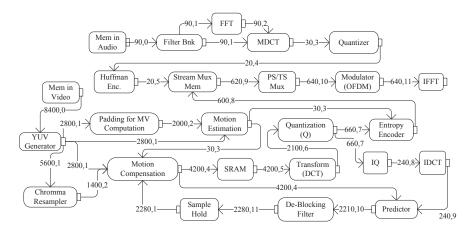

# 3.2 Unified Design Methodology for Application and MPSoC platform

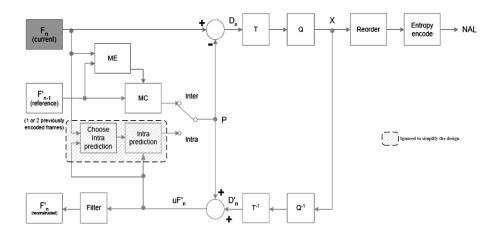

The design methodology for multiprocessor platforms with focus on unified representation of interconnection platform and application will be presented in this section. The proposed design flow is illustrated in Figure 3.2. It integrates Matlab/Simulink, HDL design and co-simulation (DSP builder), in order to raise the design abstraction level which takes a step closer to design automation. We are interested in Matlab/Simulink since it allows the exploration of task allocation results and offers the possibility for early assessment of application - platform mapping. As a running example we employ a H.264 encoder [35] as application (Figure 3.1) and SegBus as the interconnection platform.

#### 3.2.1 Tool Environment

Matlab / Simulink. Matlab Simulink Environment [79] is a tool commonly used for modeling, simulation, analysis and profiling of multi domain systems. These systems range from a simple adder to complex application like Video coding, transceiver synchronization in communication systems or

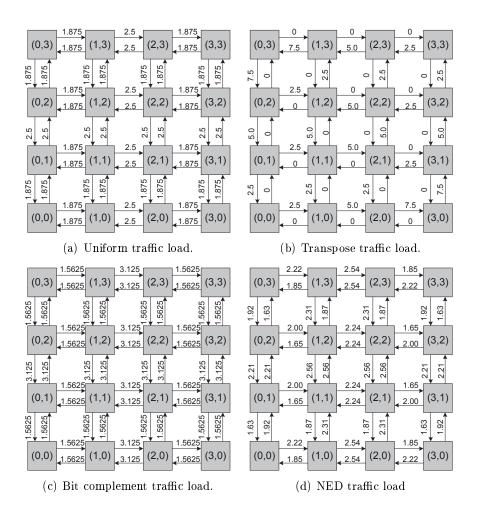

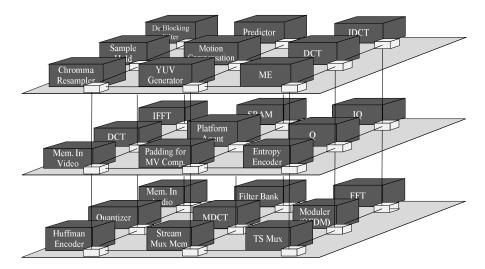

Figure 3.1: H.264 Encoder

control system design. It comprises of different block sets, libraries and programming functionalities. After the application specification, a working Simulink model can be modeled and application algorithm can be verified using different configurations and random as well as normal inputs.

Here, we use the "Video and image processing" blockset from Simulink to model the H.264 Encoder application. This blockset provides a variety of functions that can be used for modeling of Image and Video applications. The Matlab Simulink environment also supports obtaining the communication matrix necessary to compute the optimal allocation scheme for the interconnection platform.

Altera. At the time, the implementation technology for the SegBus platform is offered by Altera [42] devices. Hence, after application modeling and platform customization the flow is taken into the Quartus design environment, where previously defined functional units are mapped on actual devices. Following compilation, a simulation is performed within a Modelsim [43] framework.

**Application development.** We start by analyzing the targeted application by splitting it in processes. The interaction between these is observed in terms of input-output data-flows. In subsequent steps the top-level process is decomposed hierarchically into less complex processes and the corresponding data-flows between these processes.

The decomposition process is based on designer's experience and ends when the granularity level of the identified processes maps to existent library elements or devices that can be developed by the design team. The H.264 encoder application shown in Figure 3.1 was modeled in Simulink. The application tasks were further partitioned into number of sub-tasks in order to have enough granularity and communication complexity between tasks

Figure 3.2: Unified Design Process for Application and MPSoC platform

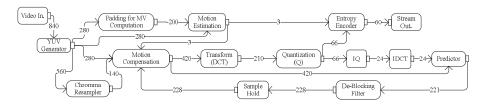

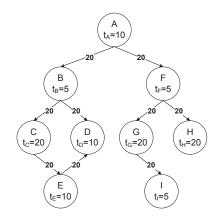

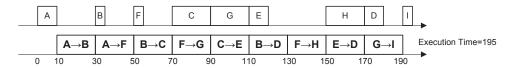

to analyze the MPSoC platform under consideration. The corresponding model is shown in Figure 3.3. The values on the edges represent the number of transaction packets for processing of one video frame, where each data packet is of same size (66 bytes).

The communication between processes is organized as a  $Packet\ SDF$  diagram [62]. The PSDF representation will be used to extract the programs

Figure 3.3: The H.264 Video encoder application model

controlling the activity (grant distribution schedule) of the SAs and of the CA [65].

The Packet SDF. A PSDF comprises mainly two elements: processes and data flows; data is, however, organized in packets. Processes transform input data packets into output ones, whereas packet flows carry data from one process to another. A transaction represents the sending of one data packet by one source process to another, target process, or towards the system output. In [62], a packet flow is a tuple of two values, P and T. P represents the number of successive, same size transactions emitted by the same source, towards the same destination; T is a relative ordering number among the (packet) flows in one given system. Thus, a flow is understood as the number of packets issued by the same process, targeting the same destination, and having the same ordering number.

A third element of the PSDF tuple characterizes the kind of the packet. The kind - a natural number I - identifies if a packet is to be routed to multiple destinations, thus establishing the modeling basis for multicasted or broadcasted transmissions as will be discussed in Chapter 4. Packet flows having same I value carry the same content of data, from the same source towards multiple destinations.

The PSDF of a certain system becomes hence a sequence of packet flows,  $\langle (P_1, T_1, I_1), \ldots, (P_n, T_n, I_n) \rangle$ ,  $P_i \neq P_j$  where  $\forall i, j \in \{1, \ldots, n\}$  and  $T_1 \leq T_2 \leq \ldots \leq T_n$ . Flows sourcing in the same node and with identical  $I_s$ , will also have identical  $I_s$ , identifying a multicast packet.

The non-strictness of the relation between T values of the above definition models the possibility of several flows to coexist at moments in the execution of the system. In the case of the SegBus platform, this most often will describe local flows, that is flows where the source and the destination are situated in the same segment. However, considering a segment number larger than 3, global flows, where the source and the destination are in different segments, are also possible to be characterized by the same ordering number. In this case, it means that the  $\mathbf{CA}$ , if possible, allows a simultaneous execution of transactions from all the "same T" global flows.

The corresponding PSDF diagram for application model in Figure 3.3 is shown in Figure 3.5. For the moment, the reader should ignore the parti-

| From / To | P0 | P1    | P2    | P3    | P4    | P5    | P6    | P7   | P8   | P9   | P10   | P11   | P12   |

|-----------|----|-------|-------|-------|-------|-------|-------|------|------|------|-------|-------|-------|

| P0        | 0  | 35840 | 17920 | 17920 | 17920 | 0     | 0     | 0    | 0    | 0    | 0     | 0     | 0     |

| P1        | 0  | 0     | 0     | 0     | 8960  | 0     | 0     | 0    | 0    | 0    | 0     | 0     | 0     |

| P2        | 0  | 0     | 0     | 12780 | 0     | 0     | 0     | 0    | 0    | 0    | 0     | 0     | 0     |

| P3        | 0  | 0     | 0     | 0     | 176   | 0     | 0     | 176  | 0    | 0    | 0     | 0     | 0     |

| P4        | 0  | 0     | 0     | 0     | 0     | 26880 | 0     | 0    | 0    | 0    | 26880 | 0     | 0     |

| P5        | 0  | 0     | 0     | 0     | 0     | 0     | 13440 | 0    | 0    | 0    | 0     | 0     | 0     |

| P6        | 0  | 0     | 0     | 0     | 0     | 0     | 0     | 4200 | 4200 | 0    | 0     | 0     | 0     |

| P7        | 0  | 0     | 0     | 0     | 0     | 0     | 0     | 0    | 0    | 0    | 0     | 0     | 0     |

| P8        | 0  | 0     | 0     | 0     | 0     | 0     | 0     | 0    | 0    | 1536 | 0     | 0     | 0     |

| P9        | 0  | 0     | 0     | 0     | 0     | 0     | 0     | 0    | 0    | 0    | 1536  | 0     | 0     |

| P10       | 0  | 0     | 0     | 0     | 0     | 0     | 0     | 0    | 0    | 0    | 0     | 0     | 14136 |

| P11       | 0  | 0     | 0     | 0     | 14539 | 0     | 0     | 0    | 0    | 0    | 0     | 0     | 0     |

| P12       | 0  | 0     | 0     | 0     | 0     | 0     | 0     | 0    | 0    | 0    | 0     | 14539 | 0     |

Figure 3.4: The communication matrix for the example

tion in segments, which is based on developments in the next sections. The processing elements  $(P0, P1, \ldots, P12)$  correspond respectively to YUV generator, Chroma resampler, Motion vector estimator units, etc. Figure 3.4 shows the number of bytes to be transferred between two  $\mathbf{FU}$ 's for the processing of one video frame.

#### 3.2.2 Application Partitioning

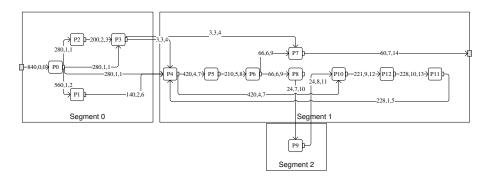

We consider that the application is already partitioned and mapped on the available devices as described in Figure 3.5. In general, this means also that all possible software procedures are already mapped within the hardware devices. However, this is not the case in Figure 3.5, where all the devices are hardware elements.

At this moment, we can extract the communication features, that is, the frequency with which the various devices communicate with each other. We group these frequencies in the so-called "communication matrix". For the application at hand, this matrix is illustrated in Figure 3.4. The matrix was obtained by using the signal dimension option in Simulink.

The matrix is fed into the *Place Tool* programme which delivers the allocation costs for various scenarios [34]. The output results of the *Place Tool* are shown in Table 3.1, where || represents the segment borders. It can be observed that performance may go down by increasing the number of segments due to increase in communication overhead. In this case, a two segment platform delivers the best performance; however, we decide to select a three segment platform, in order to analyze a more complex structure as explained in [53]. The resulting segmented application model is obtained as in Figure 3.5.

Table 3.1: The task allocation and associated cost results.

| Nr. Segs | Cost   | Allocation                                     | Improvement $(\%)$ |  |  |

|----------|--------|------------------------------------------------|--------------------|--|--|

| 1        | 233000 | 0 1 2 3 4 5 6 7 8 9 10 11 12                   | 100 (Reference)    |  |  |

| 2        | 132000 | $4\ 5\ 6\ 7\ 8\ 9\ 10\ 11\ 12\   \ 0\ 1\ 2\ 3$ | -43                |  |  |

| 3        | 137400 | 9    4 5 6 7 8 10 11 12    0 1 2 3             | -41                |  |  |

| 4        | 143100 | 9    8    4 5 6 7 10 11 12    0 1 2 3          | -39                |  |  |

Figure 3.5: PSDF application specification

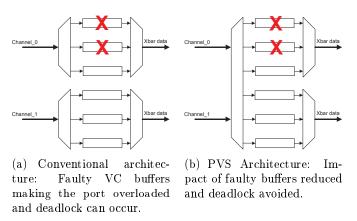

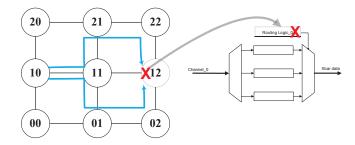

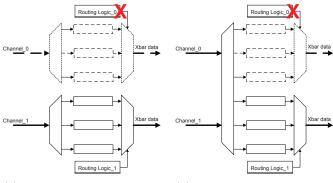

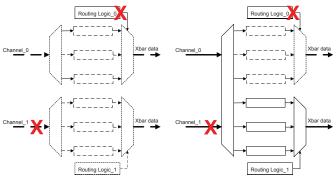

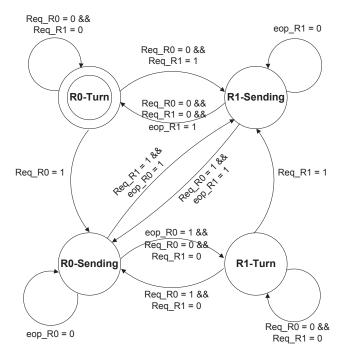

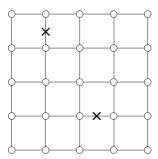

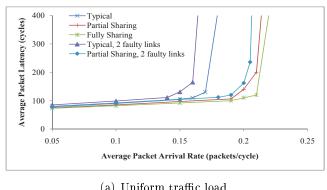

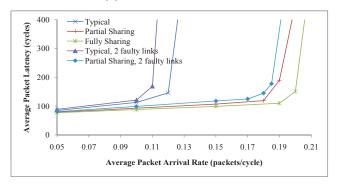

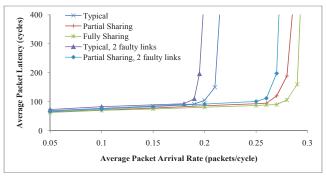

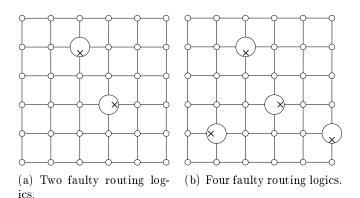

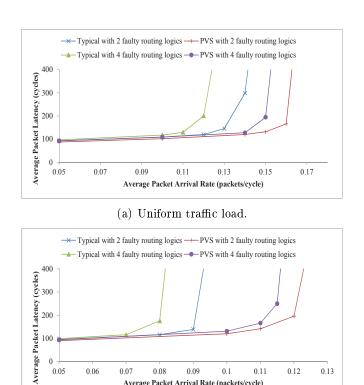

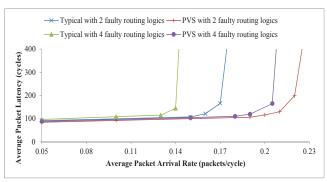

#### 3.2.3 Code Generation