#### TURUN YLIOPISTON JULKAISUJA ANNALES UNIVERSITATIS TURKUENSIS

SARJA - SER. A I OSA - TOM. 410

ASTRONOMICA - CHEMICA - PHYSICA - MATHEMATICA

# Exploration and Design of High Performance Variation Tolerant On-Chip Interconnects

by

Ethiopia Enideg Nigussie

TURUN YLIOPISTO UNIVERSITY OF TURKU Turku 2010

## **Supervisors**

Adjunct Professor Juha Plosila Professor Jouni Isoaho Professor Hannu Tenhunen Department of Information Technology University of Turku Turku, Finland

## Reviewers

Ph.D. Dinesh Pamunuwa

Center for Microsystems Engineering

Department of Engineering

Lancaster University

Lancaster, UK

Professor Olli Vainia

Professor Olli Vainio Department of Computer Systems Tampere University of Technology Tampere, Finland

# Opponent

Professor Mohammed Ismail El-Naggar Department of Electrical and Computer Engineering The Ohio State University 2015 Neil Avenue, Columbus, OH 43210 USA

ISBN 978-951-29-4363-0 (PRINT) ISBN 978-951-29-4364-7 (PDF) ISSN 0082-7002 Painosalama Oy – Turku, Finland 2010

# Abstract

Continuous technology scaling enables implementation of complex application on a single chip. As a result, there is a design paradigm shift from single-core to multicore systems and from core-centric to interconnect-centric designs, emphasizing the importance of high performance, power efficient, and reliable on-chip interconnects. In sub-90nm technologies, parameter variations are increasing and cause considerable delay variations, which creates difficulty in guaranteeing the reliability of on-chip interconnects.

In this thesis, high performance, variation tolerant and power efficient global on-chip interconnects are presented. The design and implementation of these interconnects are based on formulation and integration of different circuit level techniques. Since delay variations are inevitable, the thesis focuses on self-timed delay-insensitive communication. In this regard, design and optimization of delay-insensitive data encoding/decoding schemes as well as formulation of efficient communication protocols are performed. To compensate the delay overhead of delay-insensitive communication, high speed signaling techniques are developed and implemented. In addition, a novel high speed completion detection technique is devised and implemented to solve the performance bottleneck caused by conventional completion detection methods. A high-throughput and power efficient serial interconnect is also designed to be used as a long-range on-chip communication link.

Furthermore, an interconnect calibration technique after every power startup of a system is developed and implemented to ensure signal integrity of the interconnects despite process, we arout and aging caused variations. A runtime supply voltage and temperature variation tolerance technique is also devised and implemented for the interconnects. These PVT variation tolerance schemes make the interconnects adaptive to the effect of variations, enabling continuous and reliable operation of the interconnect.

# Acknowledgements

It gives me great pleasure to be able to express my gratitude to the people and institutions that have helped me to accomplish this research work. First and foremost, I would like to thank my supervisors Adj. Prof. Juha Plosila, Prof. Jouni Isoaho, and Prof. Hannu Tenhunen for their inspiration, guidance and support. I owe a huge debt of thanks to Adj. Prof. Juha Plosila for his invaluable and continuous guidance. His comments and criticism had a significant impact on the research presented here. I am very grateful to Prof. Jouni Isoaho for his guidance and encouragement throughout the period of my research. I am also indebted to Prof. Hannu Tenhunen for inspiring me to pursue my research in on-chip interconnects and backed me up in the final phase of the thesis. I wish to thank Prof. Olli Vainio and Ph.D. Dinesh Pamunuwa for reviewing the thesis.

The Graduate School in Electronics, Telecommunications and Automation (GETA) is gratefully acknowledged for funding my doctoral studies. This research work was financially supported by the Nokia Foundation, the Ulla Tuominen Foundation, and the Otto A. Malm Foundation.

I would like to acknowledge all my colleagues at the IT department. I am grateful to everyone who have co-authored papers with me. Special thanks go to Sampo Tuuna for co-authoring papers with me which are included in this thesis. I am thankful to D.Sc. (Tech) Johanna Tuominen and Kameswar Rao Vaddina for proof-reading part of this thesis. D.Sc. (Tech) Teijo Lehtonen deserves special thanks, he always took time to discuss any issue I brought to him and came up with practical suggestions each time.

I would like to express my deepest gratitude to my sister Konjit for her constant support, encouragement and most importantly taking care of my responsibilities at home. I am also indebted to my grand mother Abeba and my brothers Girma and Yehwalashete, who always encouraged me to follow

my ambitions, irrespective of how much they missed me. I am grateful to my finnish family Maija, Pekka and Iida who make my stay in Turku much more pleasant.

My final and most heartfelt thanks go to my husband Woubishet for his continuous support, understanding and companionship throughout my doctoral studies.

Turku, August 2010

Ethiopia Enideg Nigussie

# Contents

| A                | .bstra | .ct              |                                                       | ii   |

|------------------|--------|------------------|-------------------------------------------------------|------|

| A                | cknov  | wledgn           | nents                                                 | ii   |

| $\mathbf{L}_{i}$ | ist of | Public           | cations                                               | ⁄iii |

| $\mathbf{L}$     | ist of | Figur            | es                                                    | xii  |

| $\mathbf{L}$     | ist of | Tables           | S 2                                                   | ζvi  |

| $\mathbf{L}_{i}$ | ist of | Abbre            | eviations                                             | vii  |

| 1                | Intr   | $\mathbf{oduct}$ | ion                                                   | 1    |

|                  | 1.1    | Emerg            | gence of Interconnect-Centric Design                  | 1    |

|                  |        | 1.1.1            | Device and Interconnect Scaling                       | 2    |

|                  |        | 1.1.2            | System-on-Chip and Multicore Systems                  | 3    |

|                  |        | 1.1.3            | Network-on-Chip                                       | 4    |

|                  | 1.2    | Challe           | enges of Global On-Chip Interconnect                  | 5    |

|                  |        | 1.2.1            | Performance and Power Consumption                     | 6    |

|                  |        | 1.2.2            | Variability and Reliability                           | 7    |

|                  | 1.3    | Globa            | l On-Chip Communication Techniques                    | 8    |

|                  |        | 1.3.1            | GALS Communication                                    | 9    |

|                  |        | 1.3.2            | Self-timed Delay-Insensitive Communication            | 10   |

|                  | 1.4    | Scope            | of Thesis and Contributions                           | 10   |

|                  |        | 1.4.1            | Delay-Insensitive Current Sensing Interconnects       | 11   |

|                  |        | 1.4.2            | Completion Detection Technique to Enhance Performance | 12   |

|                  |        | 1.4.3            | High Throughput Energy Efficient Semi-Serial Link     | 13   |

|                  |        | 1.4.4            | Circuit Techniques for PVT Variation Tolerance        | 14   |

|                  | 1.5    | Relate           | ed Work                                               | 15   |

|   | 1.6  | Thesis Organization                                              |

|---|------|------------------------------------------------------------------|

| 2 | Inte | erconnect Design Techniques 19                                   |

|   | 2.1  | Handshaking Protocols                                            |

|   | 2.2  | Data Encoding Techniques                                         |

|   | 2.3  | Data Decoding Techniques                                         |

|   | 2.4  | Completion Detection Techniques                                  |

|   | 2.5  | Self-timed Components                                            |

|   | 2.6  | On-Chip Signaling Schemes                                        |

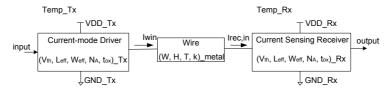

|   |      | 2.6.1 Current-Mode and Current Sensing Signaling 29              |

|   |      | 2.6.2 Voltage-Mode Signaling: Reference                          |

|   | 2.7  | On-Chip Wire Modeling                                            |

|   |      | 2.7.1 Wire Parasitic Estimation and Extraction                   |

|   |      | 2.7.2 Electrical Level Wire Modeling                             |

|   | 2.8  | Chapter Summary                                                  |

| 3 | Des  | ign of Delay-Insensitive Current Sensing Interconnects 43        |

|   | 3.1  | Level-Encoded Dual-Rail Current Sensing Interconnect 44          |

|   |      | 3.1.1 Data Encoder and Driver                                    |

|   |      | 3.1.2 Receiver, Decoder and Completion Detector 47               |

|   |      | 3.1.3 Acknowledgment Transmission 48                             |

|   |      | 3.1.4 Simulation Results and Analysis 49                         |

|   |      | 3.1.5 Effect of Crosstalk on Timing                              |

|   | 3.2  | 1-of-4 Encoded Current Sensing Interconnect                      |

|   |      | 3.2.1 Encoder and Driver                                         |

|   |      | 3.2.2 Receiver                                                   |

|   |      | 3.2.3 Decoder and Completion Detector 59                         |

|   |      | 3.2.4 Acknowledgment Transmission 61                             |

|   |      | 3.2.5 Reference Voltage-Mode Interconnects 62                    |

|   |      | 3.2.6 Simulation Results and Analysis 63                         |

|   | 3.3  | Dual-Rail Encoded Differential Current Sensing Interconnect . 69 |

|   |      | 3.3.1 Encoding and Its Implementation 71                         |

|   |      | 3.3.2 Driver, Receiver and Completion Detector                   |

|   |      | 3.3.3 Acknowledgment Transmission                                |

|   |      | 3.3.4 Simulation Results and Analysis                            |

|   | 3.4  | Chapter Summary                                                  |

|   |      |                                                                  |

| 4 | $\mathbf{Enh}$ | nancing | g Completion Detection Performance                     | 81  |

|---|----------------|---------|--------------------------------------------------------|-----|

|   | 4.1            | Delay-  | -Insensitive Bit Parallel Transmission                 | 82  |

|   | 4.2            | High-S  | Speed Completion Detection Technique                   | 85  |

|   | 4.3            | Case S  | Studies                                                | 87  |

|   |                | 4.3.1   | 1-of-4 Encoded Current Sensing Interconnect            | 88  |

|   |                | 4.3.2   | Dual-rail Encoded Differential Current Sensing Inter-  |     |

|   |                |         | connect                                                | 90  |

|   |                | 4.3.3   | Acknowledgment Transmission                            | 90  |

|   | 4.4            | Refere  | ence Cases                                             | 92  |

|   | 4.5            | Simul   | ation Results and Analysis                             | 93  |

|   |                | 4.5.1   | Wire Model                                             | 93  |

|   |                | 4.5.2   | Simulations Setup                                      | 93  |

|   |                | 4.5.3   | Performance Analysis                                   | 94  |

|   |                | 4.5.4   | Power Analysis                                         | 97  |

|   |                | 4.5.5   | Area Comparison                                        | 99  |

|   | 4.6            | Chapt   | ter Summary                                            | 100 |

| 5 | Ene            | ergy Ei | fficient Semi-Serial Interconnect                      | 101 |

|   | 5.1            | Long-   | Range Link in NoC                                      | 103 |

|   | 5.2            | High-   | Throughput Serial On-Chip Interconnect                 | 106 |

|   |                | 5.2.1   | Communication Protocol                                 | 106 |

|   |                | 5.2.2   | Serializer and Pulse Dual-Rail Encoding                | 108 |

|   |                | 5.2.3   | High-Speed Differential Pulse Current-Mode Signaling . | 110 |

|   |                | 5.2.4   | Deserializer                                           | 114 |

|   |                | 5.2.5   | Acknowledgment Transmission                            | 115 |

|   | 5.3            | Simul   | ation Results and Analysis                             | 116 |

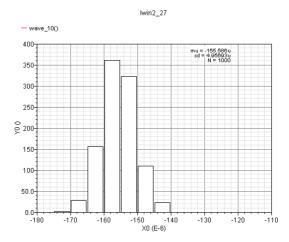

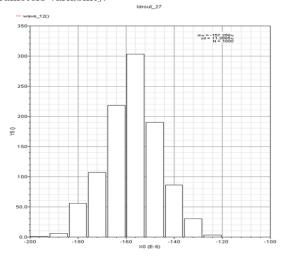

|   |                | 5.3.1   | Wire Model and Simulation Waveforms                    | 116 |

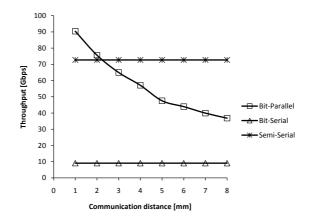

|   |                | 5.3.2   | Performance                                            | 117 |

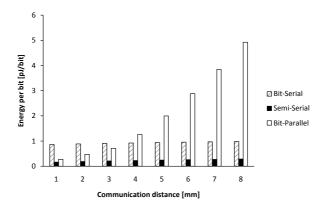

|   |                | 5.3.3   | Power and Energy Consumption                           |     |

|   | 5.4            | Fully   | Bit-Parallel vs Serial Links                           | 120 |

|   | 5.5            | Chapt   | ter Summary                                            | 123 |

| 6 | Cor            | nparis  | on of the Designed Interconnects                       | 124 |

|   | 6.1            | -       | nary of the Interconnects                              | 124 |

|   | 6.2            |         | parison of the Interconnects                           |     |

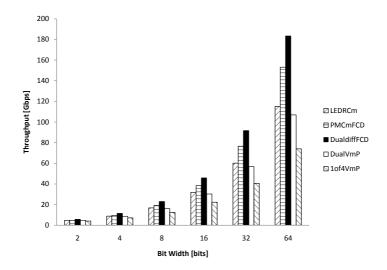

|   |                | 6.2.1   | Performance                                            |     |

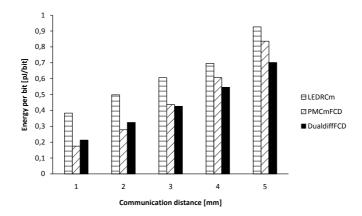

|   |                | 6.2.2   | Power Efficiency                                       |     |

|                           |       | 6.2.3   | Area                                                 |   | 130 |

|---------------------------|-------|---------|------------------------------------------------------|---|-----|

|                           | 6.3   | Chapt   | er Summary                                           |   | 130 |

| 7                         | Circ  | cuit Te | echniques for PVT Variation Tolerance                | ] | 131 |

|                           | 7.1   | Signal  | Integrity of Current Sensing Interconnect            |   | 132 |

|                           |       | 7.1.1   | Effects of Process Variation                         |   | 132 |

|                           |       | 7.1.2   | Runtime Supply Voltage and Temperature Variations    |   | 139 |

|                           | 7.2   | Post-N  | Manufacture Variation Adaptation                     |   | 141 |

|                           | 7.3   | Calibr  | ration for Process Variation Tolerance               |   | 142 |

|                           |       | 7.3.1   | Algorithm and Methodology                            |   | 142 |

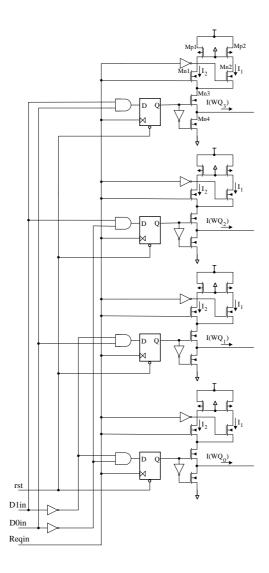

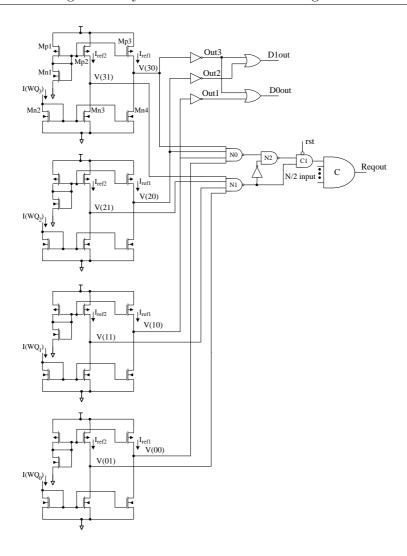

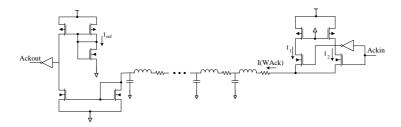

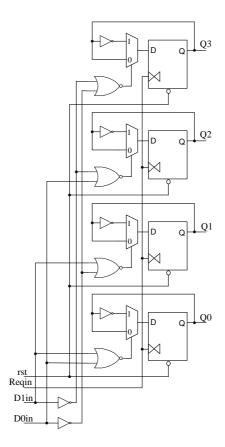

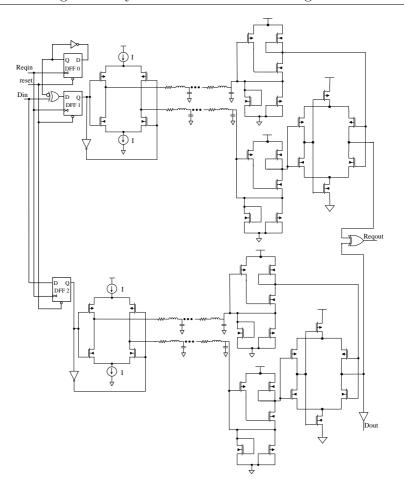

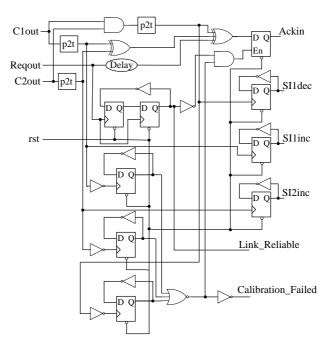

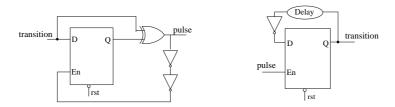

|                           |       | 7.3.2   | Reconfiguration Control and Communication Circuits   |   | 148 |

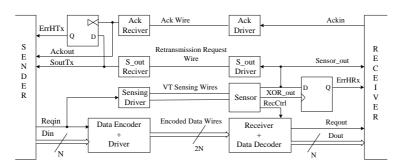

|                           | 7.4   | Runtin  | me Management of Voltage and Temperature Variations  |   | 152 |

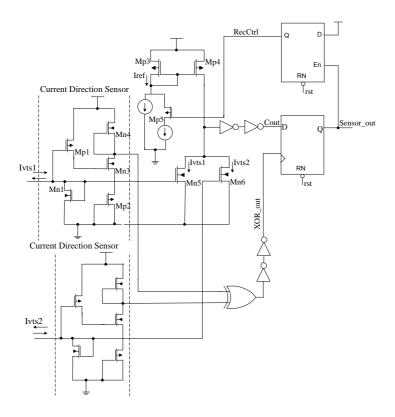

|                           |       | 7.4.1   | Sensing Effects of Voltage and Temperature Variation |   | 153 |

|                           |       | 7.4.2   | Sensor Circuit Implementation                        |   | 155 |

|                           |       | 7.4.3   | Reconfiguration and Retransmission                   |   | 156 |

|                           | 7.5   | Simula  | ation Results and Analysis                           |   | 157 |

|                           | 7.6   | Chapt   | er Summary                                           | • | 163 |

| 8                         | Con   | clusio  | ns                                                   | 1 | 164 |

|                           | 8.1   | Future  | e Work                                               |   | 166 |

|                           |       |         |                                                      |   |     |

| $\mathbf{R}_{\mathbf{c}}$ | efere | nces    |                                                      | 1 | 167 |

# List of Publications

The work discussed in this thesis is based on and extended from the publications listed below:

- E. Nigussie, J. Plosila and J. Isoaho. Monitoring and Reconfiguration Techniques for Power Supply Variation Tolerant on-Chip Links. 2010 IEEE International Symposium on Circuits and Systems (ISCAS 2010), 4 pages, May 2010, Paris, France.

- E. Nigussie, J. Plosila and J. Isoaho. Process Variation Tolerant On-Chip Communication Using Receiver and Driver Reconfiguration. 11th IEEE International Symposium on Quality Electronic Design (ISQED 2010), pages 453-460, Mar 2010, San Jose, CA, USA.

- 3. E. Nigussie, J. Plosila, S. Tuuna, J. Isoaho and H. Tenhunen. Energy Efficient Semi-Serial On-Chip Link Through Circuit Optimizations and Integration of Signaling Techniques. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, under review.

- 4. E. Nigussie, J. Plosila, S. Tuuna, J. Isoaho and H. Tenhunen. Boosting Performance of Self-Timed Delay-Insensitive Bit Parallel On-Chip Interconnects. IET Circuits, Devices and Systems Journal, under review.

- 5. E. Nigussie, J. Plosila and J. Isoaho. *High-speed Completion Detection for Current Sensing On-Chip Interconnects*. In Electronics Letters, 45(11), pages 547-548, May 2009.

- E. Nigussie, J. Plosila and J. Isoaho. Area Efficient Delay-Insensitive and Differential Current Sensing On-Chip Interconnect. In 21st IEEE International SoC Conference (SOCC 2008), Pages 143-146, Sept. 2008, Newport Beach, USA.

- E. Nigussie, J. Plosila and J. Isoaho. Current-Mode On-Chip Interconnect using Level-Encoded Two-Phase Dual-Rail Encoding. In 2007 IEEE International Symposium on Circuits and Systems (ISCAS 2007), pages 649-652, May 2007, New Orleans, USA.

- 8. E. Nigussie, T. Lehtonen, S. Tuuna, J. Plosila and J. Isoaho. *High-Performance Long NoC Link Using Delay-Insensitive Current-Mode Signaling*. In VLSI Design (Hindawi), vol. 2007, Article ID 46514, 13 pages, 2007.

The following research papers were also authored/co-authored during the course of this PhD project:

- E. Nigussie, S. Tuuna, J. Plosila, and J. Isoaho. Analysis of Crosstalk and Process Variations Effects on On-Chip Interconnects. In IEEE 2006 International Symposium on System-on-Chip, Nov. 2006, Tampere, Finland.

- 2. E. Nigussie, J. Plosila and J. Isoaho. Full-Duplex Link Implementation using Dual-Rail Encoding and Multiple-Valued Current-Mode Logic. In IEEE International Symposium on Circuits and Systems 2006 (ISCAS 2006), May 2006, Kos, Greece.

- 3. E. Nigussie, J. Plosila and J. Isoaho. *Delay-Insensitive On-Chip Communication Link using Low-Swing Simultaneous Bidirectional Signaling*. In IEEE Computer Society Annual Symposium on VLSI 2006 (ISVLSI 2006), March 2006, Karlsruhe, Germany.

- 4. E. Nigussie, J. Plosila and J. Isoaho. On Asynchronous Full-Duplex Dual-Rail Link with Multiple-Valued Current-Mode Signaling. In IEEE Circuits and Systems Society 23rd NORCHIP Conference, Nov. 2005, Oulu, Finland.

- 5. E. Nigussie, J. Plosila and J. Isoaho. *Reliable Asynchronous Links for SoC*. In IEEE 2005 International Symposium on System-on-Chip, Nov. 2005, Tampere, Finland.

- 6. L. Guang, E. Nigussie, J. Isoaho, P. Rantala and H. Tenhunen. *Interconnection Alternatives for Hierarchical Monitoring Communication in Parallel System-on-Chip.* In Microprocessors and Microsystems:

- Embedded Hardware Design Journal, Elsevier, Vol. 34, No. 5, Aug. 2010.

- L. Guang, E. Nigussie, P. Rantala, J. Isoaho and H. Tenhunen. Hierarchical Agent Monitoring Design Approach towards Self-Aware Systems. In ACM Transactions in Embedded Computing Systems (TECS), 9(3), pages 25:1-25:24, Feb. 2010.

- 8. L. Guang, E. Nigussie and H. Tenhunen. Run-time Communication By-passing for Energy-Efficient, Low-Latency Per-Core DVFS on Network-on-Chip. To appear in 23rd IEEE International SoC Conference (SOCC 2010), Nevada, USA.

- 9. L. Guang, E. Nigussie and H. Tenhunen. System-Level Exploration of Run-Time Clusterization for Energy-Efficient On-Chip Communication. In 2nd international workshop on Network-on-chip architectures, held in conjunction with 42nd Annual IEEE/ACM International Symposium on Microarchitecture (MICRO-42), Dec 2009, New York, USA.

- L. Guang, E. Nigussie, L. Koskinen, and H. Tenhunen. Autonomous DVFS on Supply Islands for Energy-constrained NoC Communication. In International Conference on Architecture of Computing Systems 2009, Springer Lecture Notes in Computer Science (LNCS), 5545, Mar 2009.

- K. R. Vaddina, E. Nigussie, P. Liljeberg and J. Plosila. Self-Timed Thermal Sensing and Monitoring of Multicore Systems. In 12th IEEE Symposium on Design and Diagnostics of Electronic Systems, April 2009, Czech.

- S. Tuuna, E. Nigussie, J. Isoaho, and H. Tenhunen. Analysis of Delay Variation in Encoded On-Chip Bus Signaling under Process Variation. In 21st International Conference on VLSI Design, Jan. 2008, Hyderabad, India.

- L. Guang, P. Liljeberg, E. Nigussie and H. Tenhunen. A Review of Dynamic Power Management Methods in NoC Under Emerging Design Considerations. In IEEE Norchip 2009, Nov 2009, Trondehim, Norway.

- 14. W. Yin, L. Guang, E. Nigussie, P. Liljeberg, J. Isoaho and H. Tenhunen.

Architecture Exploration of Per-Core DVFS for Energy-Constrained On-

- Chip Networks. In 12th Euromicro Conference on Digital System Design (DSD 2009), Aug 2009.

- K. R. Vaddina, L. Guang, E. Nigussie, P. Liljeberg and J. Plosila. Online Distributed Thermal Sensing and Monitoring of Multicore Systems. In IEEE 26th NORCHIP Conference, Nov. 2008, Tallinn, Estonia.

- L. Guang, P. Rantala, E. Nigussie, J. Isoaho, and H. Tenhunen. Low-latency and Energy-efficient Monitoring Interconnect for Hierarchical-agent-monitored NoCs. In IEEE 26th NORCHIP Conference, Nov. 2008, Tallinn, Estonia.

- 17. L. Guang, A. W. Yin, P. Rantala, E. Nigussie, P. Liljeberg, J. Isoaho and H. Tenhunen. *Hierarchical Power Monitoring for On-chip Networks*. In Proceedings of Work in Progress Session in Euromicro PDP 2009 Conference, Feb 2009.

- A. W. Yin, L. Guang, P. Liljeberg, P. Rantala, E. Nigussie, J. Isoaho and H. Tenhunen. *Hierarchical Agent Based NoC with Dynamic Online* Services. In The 4th IEEE Conference on Industrial Electronics and Applications (ICIEA 2009), May 2009.

- A. W. Yin, L. Guang, P. Liljeberg, P. Rantala, E. Nigussie, J. Isoaho and H. Tenhunen. Hierarchical Agent Architecture for Scalable NoC Design with Online Monitoring Services. 1st International Workshop on Network on Chip Architectures (NoCArc) held in conjunction with 41st Annual IEEE/ACM International Symposium on Microarchitecture (MICRO-41), Nov. 2008.

# List of Figures

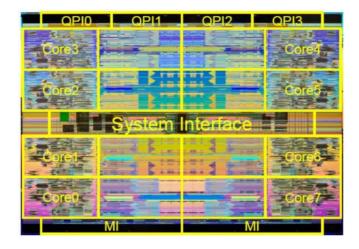

| 1.1  | Intel's 45nm 8-core Xeon-EX processor [5]                   | 4  |

|------|-------------------------------------------------------------|----|

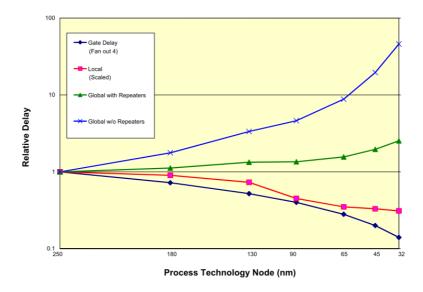

| 1.2  | Delay comparison [105]                                      | 7  |

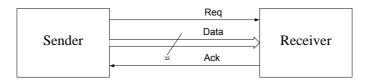

| 2.1  | Push channel                                                | 20 |

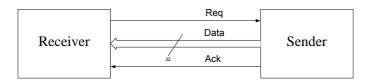

| 2.2  | Pull channel                                                | 20 |

| 2.3  | Four-phase handshaking protocol                             | 21 |

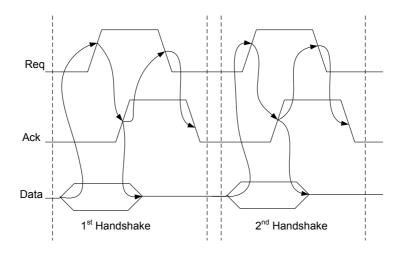

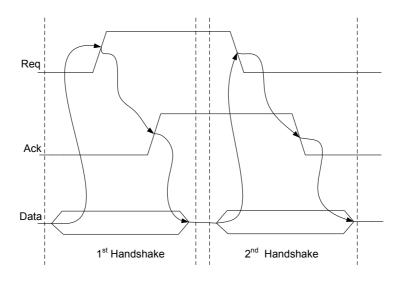

| 2.4  | Two-phase handshaking protocol                              | 22 |

| 2.5  | Delay-insensitive push channel                              | 23 |

| 2.6  | Four-phase dual-rail encoded transmission                   | 24 |

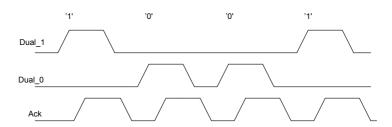

| 2.7  | Two-phase dual-rail encoded transmission                    | 24 |

| 2.8  | Four-phase 1-of-4 encoded transmission                      | 25 |

| 2.9  | Two-phase 1-of-4 encoded transmission                       | 25 |

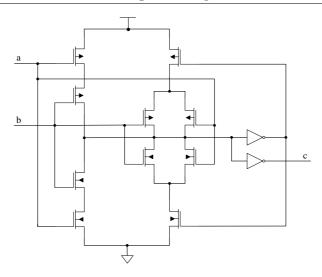

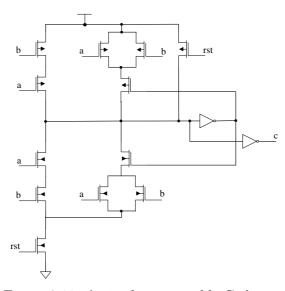

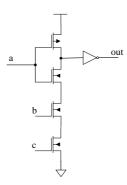

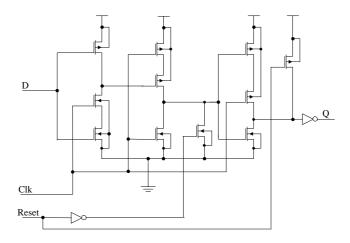

| 2.10 | Transistor level implementation of a 2-input C-element      | 28 |

| 2.11 | Active-low resettable C-element                             | 28 |

| 2.12 | 3-input upper asymmetric C-element                          | 29 |

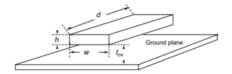

| 2.13 | Single microstrip wire                                      | 35 |

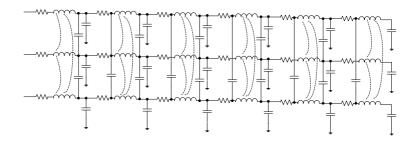

| 2.14 | Distributed RLC wire model with coupling                    | 42 |

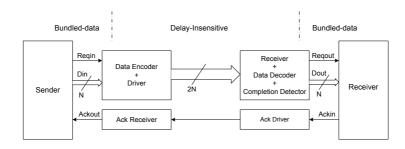

| 3.1  | Bundled-data $\Leftrightarrow$ delay-insensitive conversion | 44 |

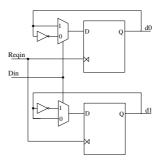

| 3.2  | Conventional two-phase dual-rail encoder                    | 45 |

| 3.3  | Conventional two-phase dual-rail decoder and completion de- |    |

|      | tector                                                      | 45 |

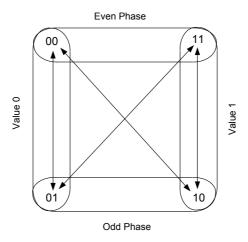

| 3.4  | Transitions between LEDR code                               | 46 |

| 3.5  | Protocol conversion                                         | 47 |

| 3.6  | LEDR encoded current sensing on-chip interconnect           | 48 |

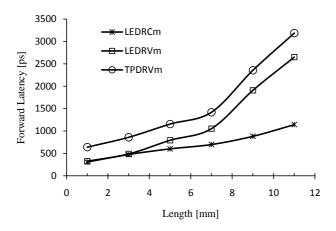

| 3.7  | Forward latency of $LEDRCm$ , $LEDRVm$ and $TPDRVm$         | 50 |

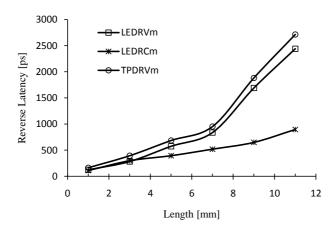

| 3.8  | Backward latency of $LEDRCm$ , $LEDRVm$ and $TPDRVm$        | 50 |

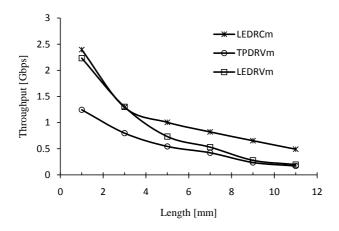

| 3.9  | Throughput of $LEDRCm$ , $LEDRVm$ and $TPDRVm$              | 51 |

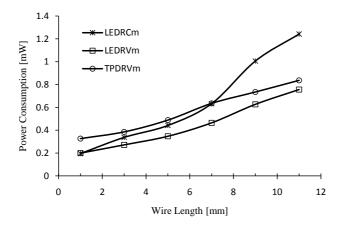

| 3.10 | Power consumption of $LEDRCm$ , $LEDRVm$ and $TPDRVm$                                  | 52 |

|------|----------------------------------------------------------------------------------------|----|

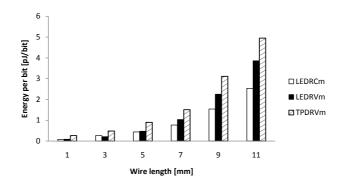

| 3.11 | Energy per bit dissipation of $\mathit{LEDRCm},\mathit{LEDRVm}$ and $\mathit{TPDRVm}.$ | 52 |

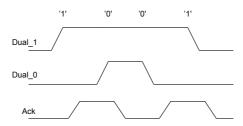

| 3.12 | Simulation waveforms of $LEDRCm$ interconnect                                          | 53 |

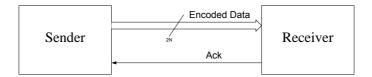

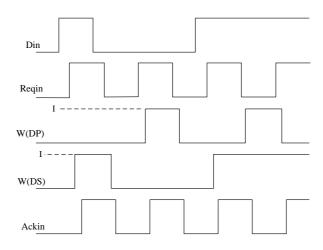

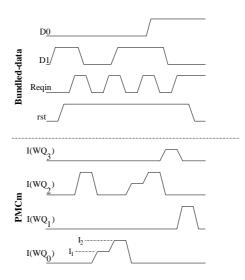

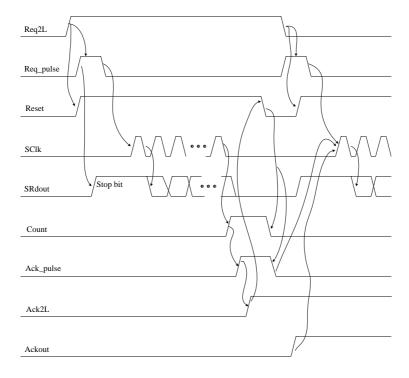

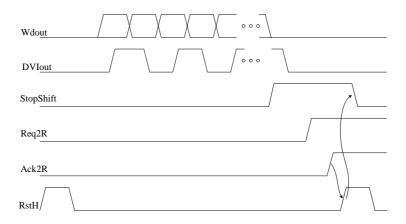

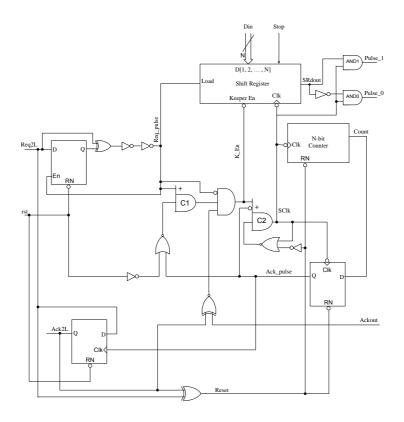

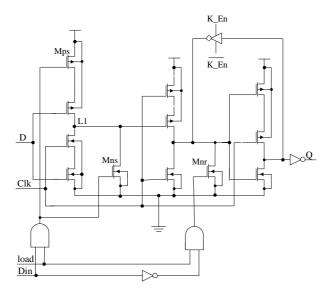

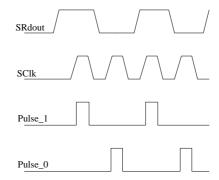

| 3.13 | Communication protocol of <i>PMCm</i>                                                  | 56 |

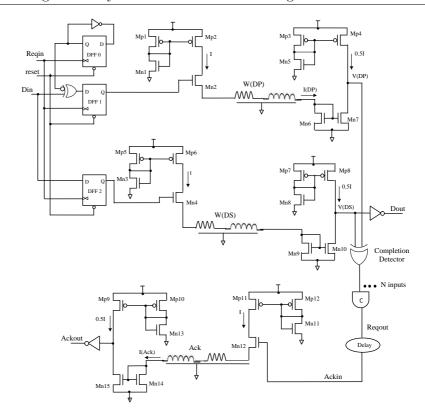

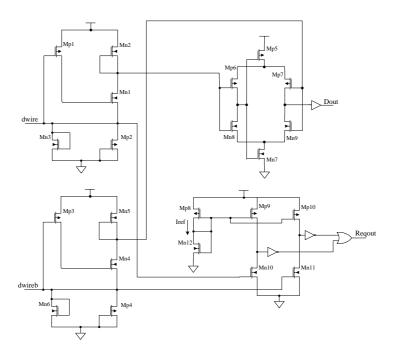

| 3.14 | Encoder and driver of <i>PMCm.</i>                                                     | 58 |

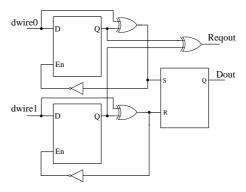

| 3.15 | Decoder and completion detector of <i>PMCm.</i>                                        | 60 |

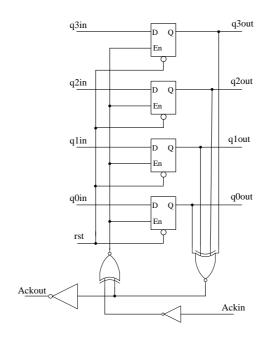

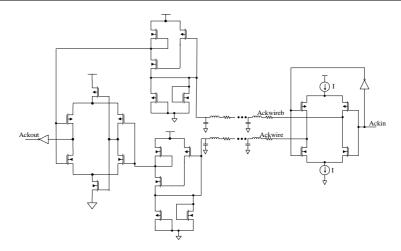

| 3.16 | Acknowledgment transmission of <i>PMCm</i>                                             | 61 |

| 3.17 | Encoder of TPVm                                                                        | 63 |

| 3.18 | Pipeline stage, acknowledgment driver and receiver of TPVmP.                           | 64 |

| 3.19 | Decoder and completion detector of TPVm                                                | 64 |

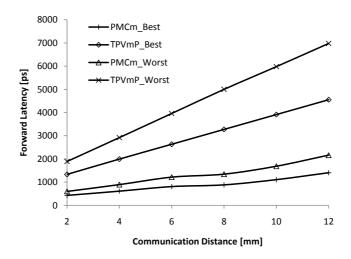

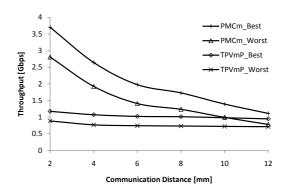

| 3.20 | Forward latency of 1-of-4 encoded interconnects                                        | 65 |

| 3.21 | Throughput of 1-of-4 encoded interconnects                                             | 66 |

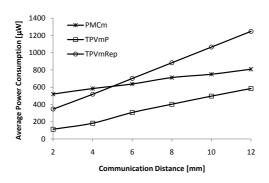

| 3.22 | Power consumption of 1-of-4 encoded interconnects                                      | 67 |

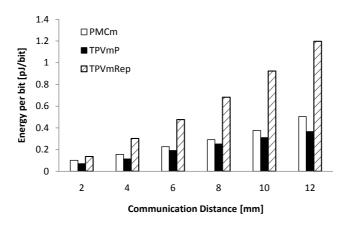

| 3.23 | Energy per bit dissipation of 1-of-4 encoded interconnects                             | 68 |

| 3.24 | Crosstalk effect in latency of $PMCm$ and $TPVmP$                                      | 69 |

| 3.25 | Crosstalk effect in throughput of $PMCm$ and $TPVmP$                                   | 69 |

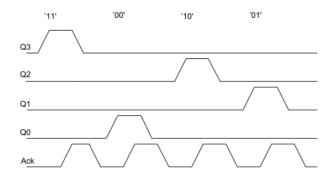

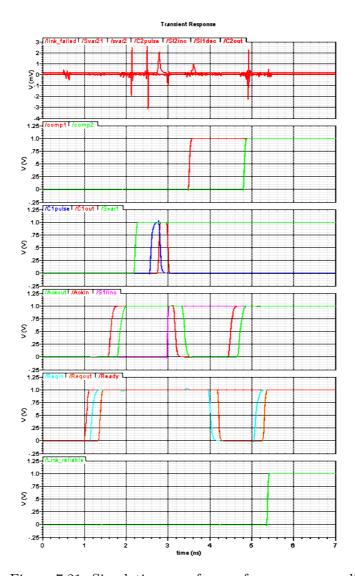

| 3.26 | Simulation waveforms of <i>PMCm</i>                                                    | 70 |

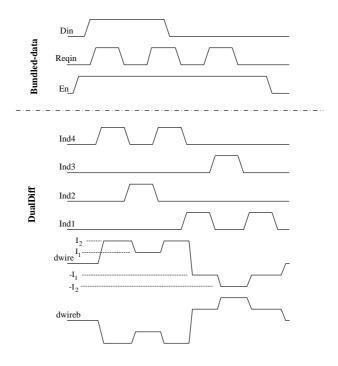

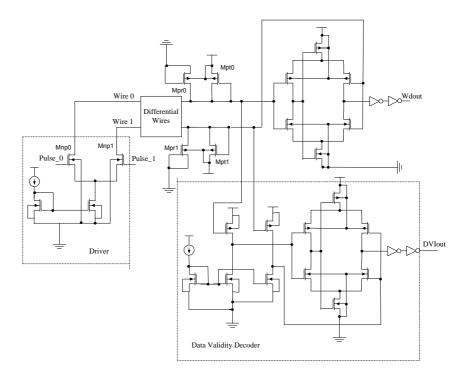

| 3.27 | Communication protocol of $\textit{Dualdiff}$ interconnect                             | 72 |

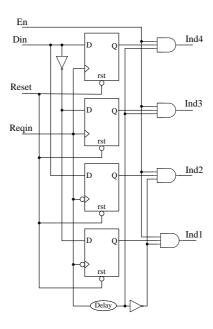

| 3.28 | Encoder of <i>Dualdiff</i> interconnect                                                | 73 |

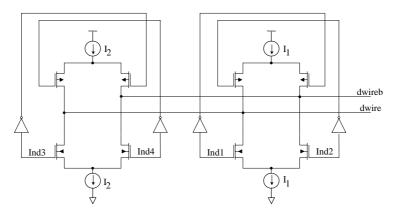

| 3.29 | Driver of Dualdiff interconnect                                                        | 73 |

| 3.30 | Receiver and completion detector of $\mathit{Dualdiff}$ interconnect                   | 75 |

| 3.31 | Acknowledgment transmission of $\textit{Dualdiff}$ interconnect                        | 76 |

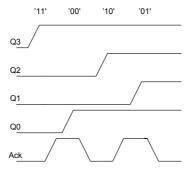

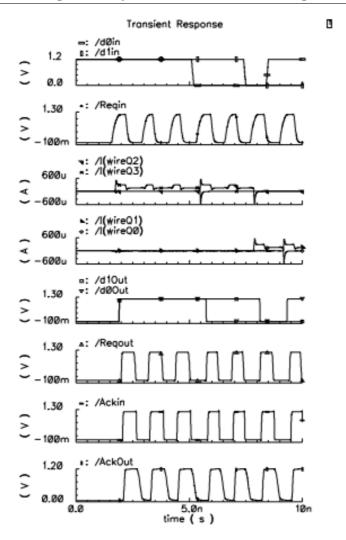

| 3.32 | Simulation waveforms of <i>Dualdiff</i>                                                | 77 |

| 3.33 | LEDR encoded differential interconnect                                                 | 78 |

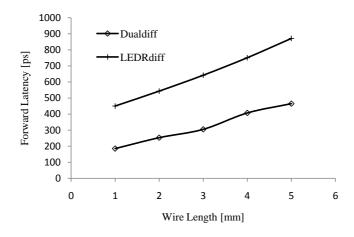

| 3.34 | Forward latency of <i>Dualdiff</i> and <i>LEDRdiff</i>                                 | 79 |

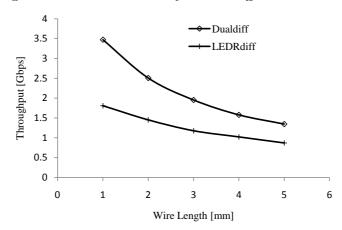

| 3.35 | Throughput of $Dualdiff$ and $LEDRdiff$                                                | 79 |

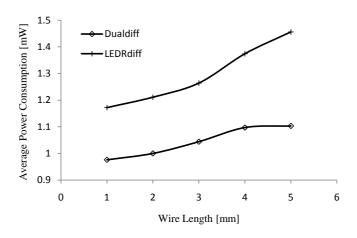

| 3.36 | Power consumption of $\textit{Dualdiff}$ and $\textit{LEDRdiff}$                       | 80 |

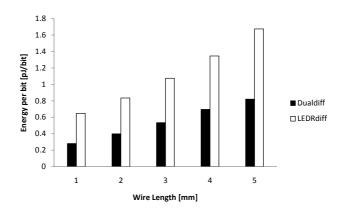

| 3.37 | Energy per bit dissipation of Dualdiff and LEDRdiff                                    | 80 |

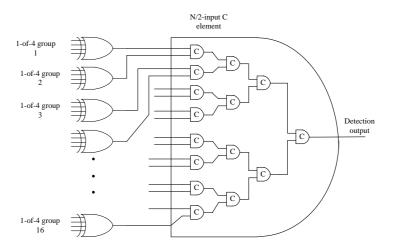

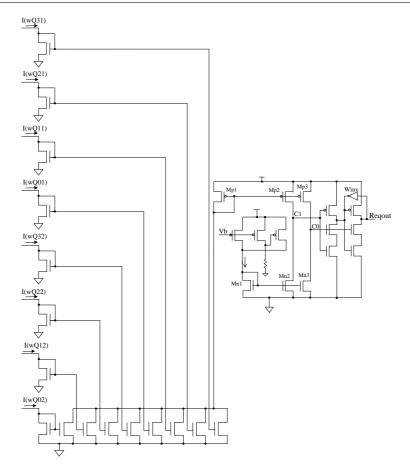

| 4.1  | Completion detector of 32-bit Two-Phase 1-of-4 Transmission $$ .                       | 83 |

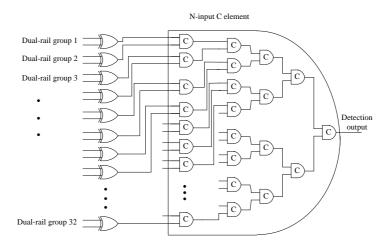

| 4.2  | Completion detector of 32-bit Two-Phase Dual-Rail Transmission                         | 84 |

| 4.3  | Completion detection in a pipelined voltage-mode link                                  | 84 |

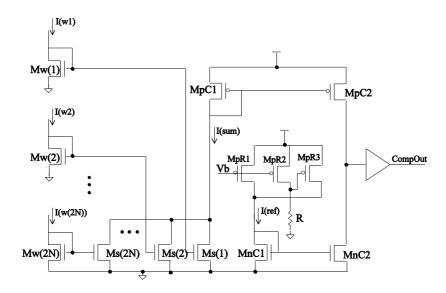

| 4.4  | High-speed completion detection circuit                                                | 87 |

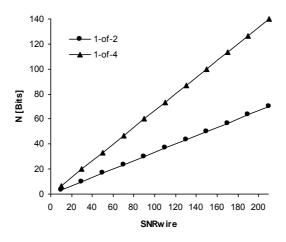

| 4.5  | Bit-width versus SNR of a wire for a reliable detection                                | 87 |

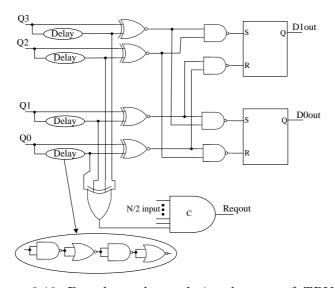

| 4.6  | Completion detection circuit of 4-bit $PMCmFCD$ link                                   | 89 |

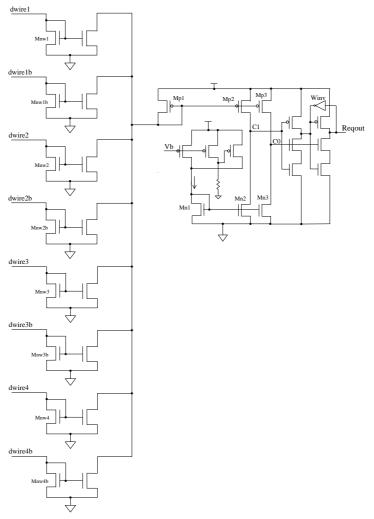

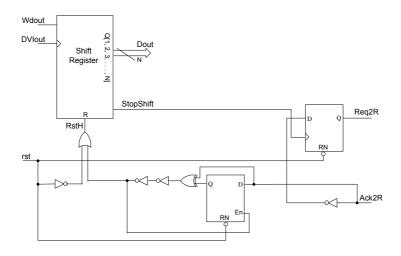

| 4.7  | Completion detection circuit of 4-bit $\textit{DualdiffFCD}$ link                      | 91 |

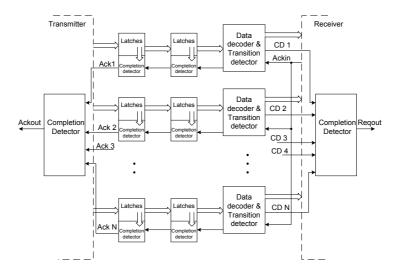

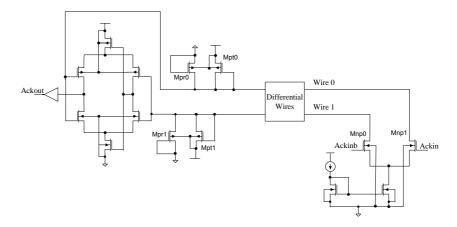

| 4.8  | Acknowledgment signal transmission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 92  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

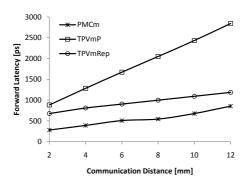

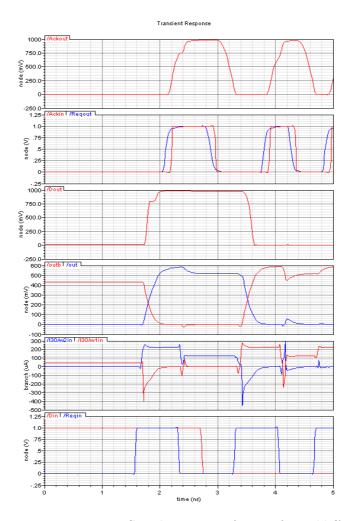

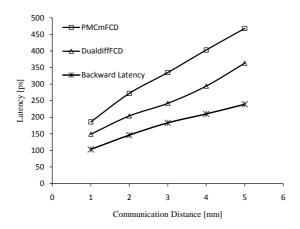

| 4.9  | Latency of links with high-speed completion detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 95  |

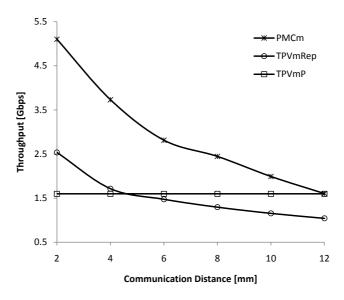

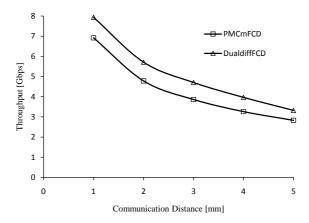

| 4.10 | Throughput of links with high-speed completion detection. $$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 95  |

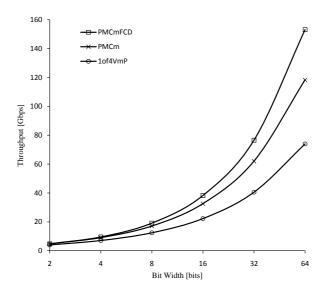

| 4.11 | Throughput of two-phase 1-of-4 encoded 2mm interconnects. $% \left( 1\right) =\left( 1\right) \left( 1\right) \left($ | 96  |

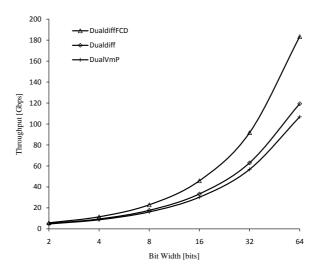

| 4.12 | Throughput of two-phase dual-rail encoded 2mm interconnects.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 97  |

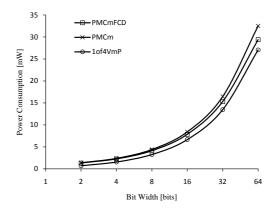

| 4.13 | Power consumption of 1-of-4 encoded 2mm interconnects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 98  |

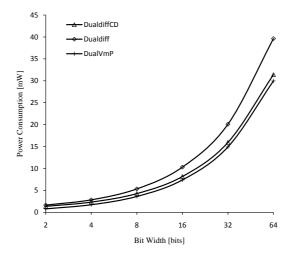

| 4.14 | Power consumption of dual-rail 2mm encoded interconnects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 98  |

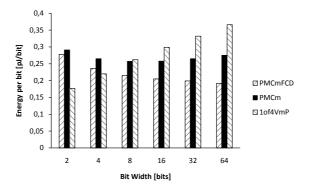

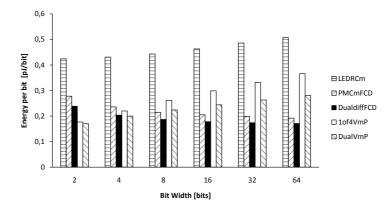

| 4.15 | Energy per bit dissipation of 1-of-4 encoded 2mm Links                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 99  |

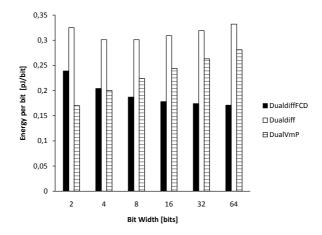

| 4.16 | Energy per bit dissipation of dual-Rail encoded 2mm Links $$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 99  |

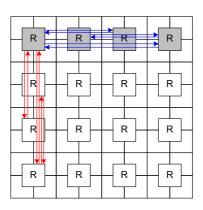

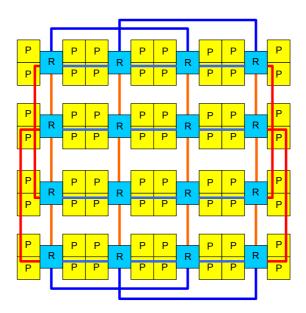

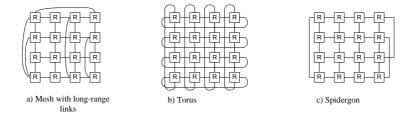

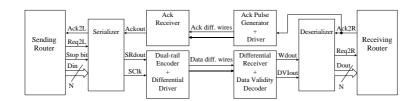

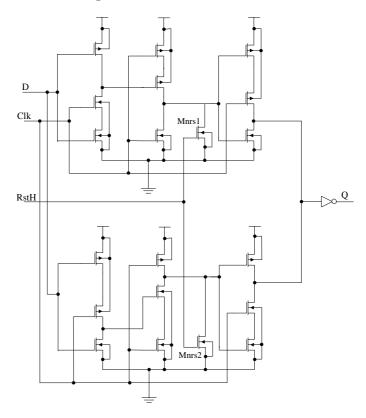

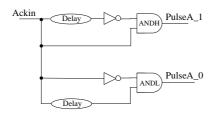

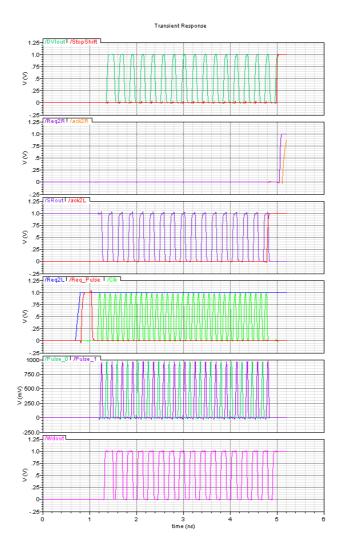

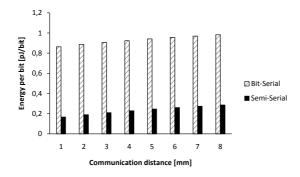

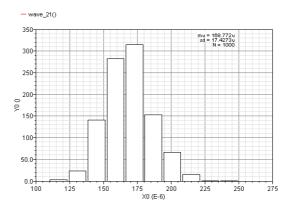

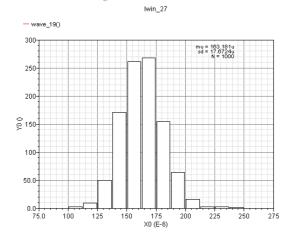

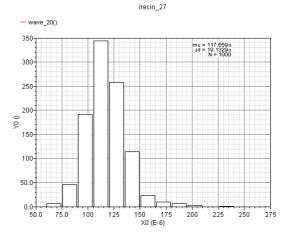

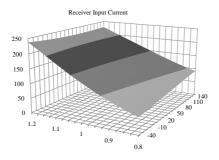

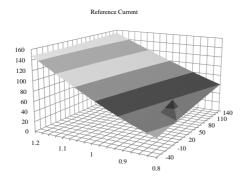

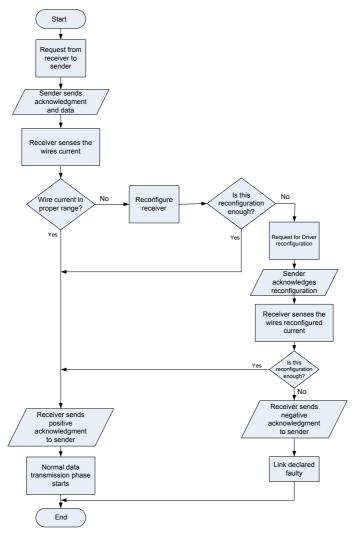

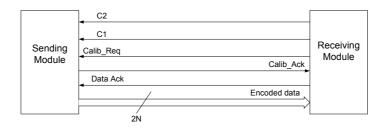

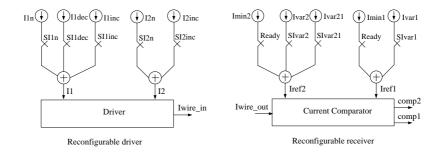

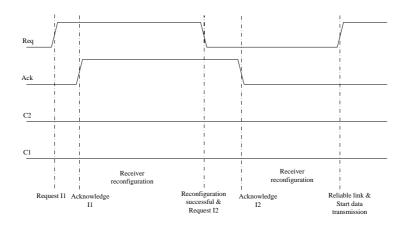

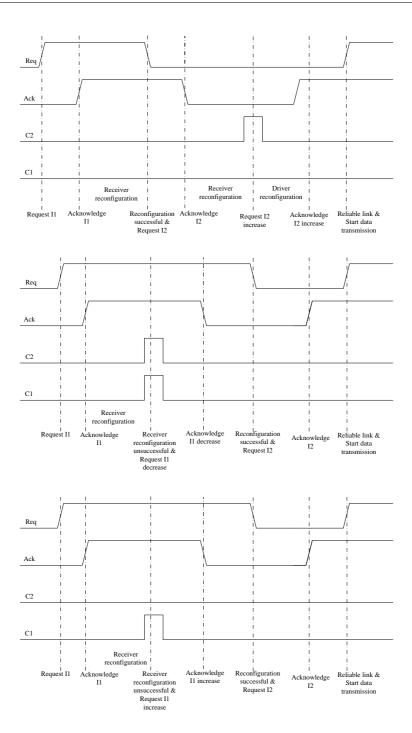

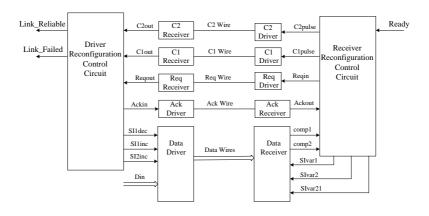

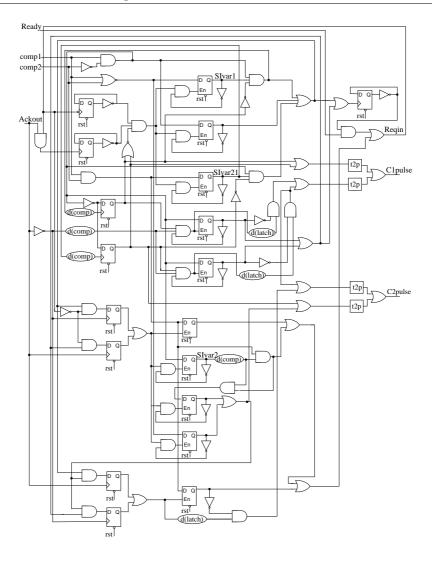

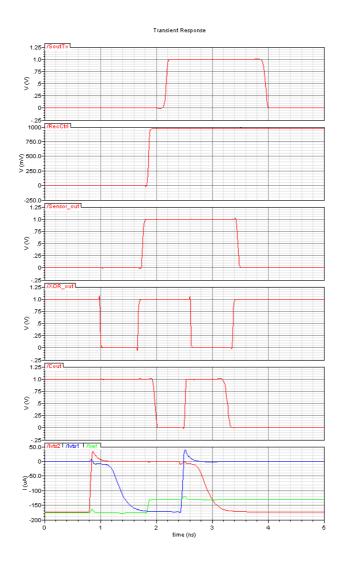

| 5.1  | 64 nodes flattened butterfly topology [67]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 104 |